一種采用自適應跟蹤的ZOOMADC

本發明屬于集成電路設計領域,特別涉及一種模數轉換器。

背景技術:

1、模數轉換器(analog-to-digital?converter,adc)實現模擬信號到數字信號的轉換,是模擬系統與數字系統接口的關鍵部件,在消費電子、工業電子等應用中有著重要的作用。過采樣adc是高精度應用中常用的一種adc架構。如圖1所示,過采樣adc通常由adc核心和數字濾波器構成,數字濾波器對adc核心轉換得到的數字碼進行濾波處理,以實現提高精度等作用。

2、在理想情況下,adc的輸出等于輸入信號,即dout=vin。然而由于adc核心的非理想性,在將模擬信號轉換成數字信號的過程中,會引入多種誤差,如失調電壓、噪聲、量化誤差等。可用公式表達為:

3、dout=vin+vos+vn+q

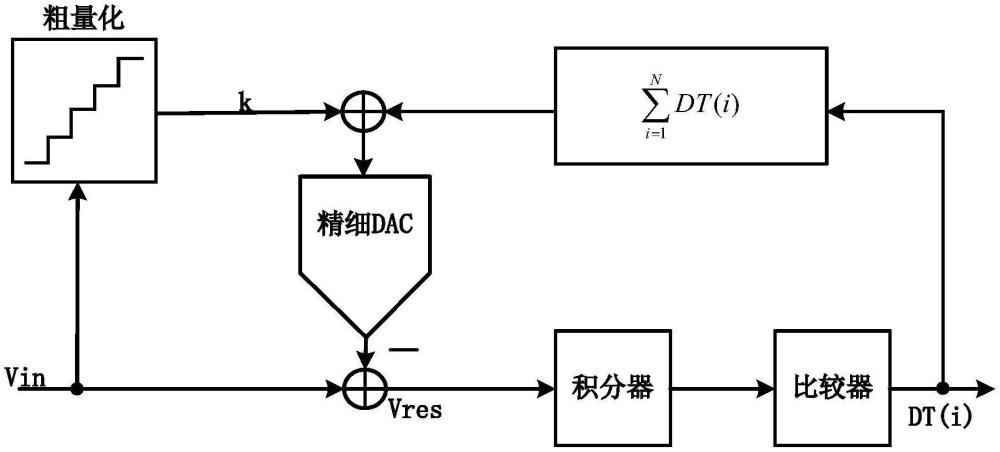

4、其中,dout為數字輸出信號,vin為模擬輸入信號,vos為失調電壓,vn為噪聲,q為量化誤差。一種常見的過采樣adc是δσ(sigma-delta)調制器。但傳統的高精度δσ調制器的功耗較高,需要使用低功耗技術進行改進。zoom?adc(縮放型adc)在δσ調制器的基礎上結合了sar?adc(successive?approximation?register?adc,逐次逼近寄存器型adc)的優點,擁有高精度、低功耗、低噪聲等優點,擁有良好的應用前景,結構框圖如圖2所示。

5、zoom?adc的轉換步驟分為粗量化和精細量化,輸入信號進入zoom?adc,首先進行粗量化。由粗量化結果決定精細量化的參考基準電壓范圍(vrefn、vrefp)。δσ調制器用得到的vref作為參考基準電壓處理信號,完成整個zoom?adc量化。

6、參考基準電壓與輸入信號的差值是δσ調制器中積分器的輸入。zoom?adc通過粗量化為δσ調制器選擇參考基準電壓縮小vrefp與vrefn之間的范圍,降低了δσ調制器中積分器的輸入信號范圍,因此積分器可以使用更大的增益系數。但由于sar?adc的非理想因素,例如電容或者比較器的噪聲和失調電壓,粗量化選擇的參考電壓偏離輸入信號,如圖4所示,導致δσ調制器超量程,從而降低系統精度。

7、為了解決這個問題,兩個方法被提出,一是降低sar?adc的分辨率,二是over-ranging(擴大量程)。參考文獻“y.chae,k.souri?and?k.a.a.makinwa,"a6.3μw?20bincremental?zoom-adc?with?6ppm?inl?and?1μv?offset,"2013ieee?internationalsolid-state?circuits?conference?digest?of?technical?papers,san?francisco,ca,usa,2013,pp.276-277”“b.f.sebastiano,r.van?veldhoven?and?k.a.a.makinwa,"a1.65mw?0.16mm2?dynamic?zoom-adc?with?107.5db?dr?in?20khz?bw,"2016ieeeinternational?solid-state?circuits?conference(isscc),san?francisco,ca,usa,2016,pp.282-283”“e.eland,s.karmakar,b.r.van?veldhoven?and?k.makinwa,"a440μw,109.8db?dr,106.5db?sndr?discrete-time?zoom?adc?with?a?20khz?bw,"2020ieee?symposium?on?vlsi?circuits,honolulu,hi,usa,2020,pp.1-2”“y.liu?etal.,"a?4.96μw?15b?self-timed?dynamic-amplifier-based?incremental?zoom?adc,"2022ieee?international?solid-state?circuits?conference(isscc),san?francisco,ca,usa,2022,pp.170-172”都使用了第一種方法,sar?adc的分辨率只有5位或者6位,較低的分辨率讓粗量化選擇的vrefp與vrefn之間的范圍較大。即使因為非理想因素影響粗量化選擇參考基準電壓,也能夠使輸入信號被包含在vrefp與vrefn范圍內,保證δσ調制器的正常工作。zoom?adc的分辨率取決于量化區間[vrefp,vrefn]的范圍大小,以及調制器的階數和過采樣率,較低的sar?adc分辨率會降低精度,要達到同樣的精度要更高的osr(oversamplingratio,過采樣率),導致積分器的帶寬要求增大,同時增加adc的功耗。上述四篇參考文獻也提到了擴大量程的方法,方法如圖5所示。

8、引入超量程因子m,讓粗量化選擇的參考電壓擴大范圍,由(vrefp-vrefn)擴大到m*(vrefp-vrefn),使信號能夠被包含在選擇的參考電壓的范圍內,擴大后參考基準電壓變為:

9、vrefp=(k+m+1)·vlsb

10、vrefn=(k-m)·vlsb

11、粗量化選擇的參考基準電壓范圍擴大放寬了對sar?adc的精度要求,提高了系統的魯棒性。但是,由于sar?adc的轉換速度有限,在粗量化選擇δσ調制器參考基準電壓期間,輸入信號仍在變化,可能移出選擇的參考基準電壓范圍,使得δσ調制器無法正常工作。擴大量程增加了δσ調制器中積分器的輸入范圍。積分環路因為更大的輸入導致不穩定,同時也對積分器的線性度提出了更高的要求。

12、zoom?adc結合了δσ調制器和sar?adc的優點,具有高精度、低功耗、低噪聲等優點。但是由于sar?adc的噪聲和失調電壓等非理想因素,導致精細量化期間的輸入信號超量程,zoom?adc的精度受到抑制。為了解決這一問題,一種方式是降低sar?adc的精度,但是δσ調制器需要的osr更高,對積分器的帶寬要求更高。另外一種方式是增大δσ調制器參考基準電壓范圍,但使得δσ調制器的積分器的輸出信號擺幅增大,線性度要求提高,設計難度增加。

技術實現思路

1、為解決上述技術問題,本發明提出一種采用自適應跟蹤的zoom?adc,通過將lsb(least?significant?bit,最低有效位)重復比較后的數字碼字累加后反饋到跟蹤電容陣列上,解決zoom?adc的超量程誤差問題。

2、本發明采用的技術方案之一為:一種采用自適應跟蹤的zoom?adc,粗量化adc電容陣列、跟蹤電容陣列、積分器、比較器以及數字邏輯模塊;zoom?adc一個完整的工作周期依次包括三個部分:采樣、粗量化轉換周期、自適應跟蹤轉換周期;

3、在采樣期間,粗量化adc電容陣列對輸入信號進行采集;

4、在粗量化轉換周期,粗量化adc電容陣列、比較器、數字邏輯參與粗量化過程;比較器對粗量化adc電容陣列的上極板電平進行量化后,通過數字邏輯模塊寄存并傳輸給粗量化adc電容陣列的下極板,生成下一個粗量化過程的殘差電壓;該粗量化過程進行m次,m為粗量化位數;

5、在自適應跟蹤轉換周期,zoom?adc采用自適應跟蹤轉換,該周期包括osr次自適應跟蹤轉換過程;跟蹤電容陣列、積分器、比較器以及數字邏輯模塊參與每一次自適應跟蹤轉換過程;跟蹤電容陣列上極板的電平在積分器上積分后,通過比較器量化,再通過數字邏輯模塊寄存得到數字碼dt,通過對dt的數字域積分后,將該值傳遞給跟蹤電容陣列的下極板,在上極板生成新的殘差電壓參與下一次自適應跟蹤轉換過程;

6、粗量化得到的數字碼字與自適應跟蹤轉換數字碼字dt進行對齊與重組,最終得到zoom?adc的數字輸出。

7、本發明采用的技術方案之二為:一種采用自適應跟蹤的zoom?adc,包括:粗量化adc電容陣列、跟蹤電容陣列、積分器、比較器以及數字邏輯模塊;zoom?adc一個完整的工作周期依次包括三個部分:采樣、粗量化轉換周期、自適應跟蹤轉換周期;

8、在采樣期間,粗量化adc電容陣列對輸入信號進行采集;

9、在粗量化轉換周期,粗量化adc電容陣列、比較器、數字邏輯參與粗量化過程;比較器對粗量化adc電容陣列的上極板電平進行量化后,通過數字邏輯寄存并傳輸給粗量化adc電容陣列的下極板,生成下一個粗量化過程的殘差電壓;該粗量化過程進行m次,m為粗量化位數;

10、在自適應跟蹤轉換周期,zoom?adc采用自適應跟蹤轉換,該周期包括osr次自適應跟蹤轉換過程;跟蹤電容陣列、積分器、比較器以及數字邏輯參與每一次自適應跟蹤轉換過程;跟蹤電容陣列上極板的電平在積分器上積分后,通過比較器量化,再通過數字邏輯模塊寄存得到數字碼dt,通過對dt累加處理轉換為二進制信號,將該二進制信號傳遞給跟蹤電容陣列的下極板,在上極板生成新的殘差電壓參與下一次精量化轉換;

11、粗量化得到的數字碼字與自適應跟蹤轉換數字碼字dt進行對齊與重組,最終得到zoom?adc的數字輸出。

12、本發明采用的技術方案之三為:一種采用自適應跟蹤的zoom?adc,包括:電容陣列、積分器、比較器以及數字邏輯模塊;zoom?adc一個完整的工作周期依次包括三個部分:采樣、粗量化轉換周期、自適應跟蹤轉換周期;

13、在采樣期間,電容陣列對輸入信號進行采集;

14、在粗量化轉換周期,電容陣列、比較器、數字邏輯模塊參與粗量化過程;比較器對電容陣列的上極板電平進行量化后,通過數字邏輯模塊寄存并傳輸給粗量化電容陣列的下極板,生成下一個粗量化過程的殘差電壓;該過程進行m次,m為粗量化位數;

15、在自適應跟蹤轉換周期,zoom?adc采用自適應跟蹤轉換,該周期包括osr次自適應跟蹤轉換過程;電容陣列、積分器、比較器以及數字邏輯模塊參與每一次自適應跟蹤轉換過程;電容陣列上極板的電平在積分器上積分后,通過比較器量化,再通過數字邏輯模塊寄存得到數字碼dt,通過對dt與粗量化碼字在數字域進行加法處理,將該值傳遞給電容陣列的下極板,在上極板生成新的殘差電壓參與下一次自適應跟蹤轉換過程;

16、粗量化得到的數字碼字與自適應跟蹤轉換數字碼字dt進行對齊與重組,最終得到zoom?adc的數字輸出。

17、本發明的有益效果:本發明提出的zoom?adc,通過增加跟蹤電容陣列,對sar?adc量化后的lsb位重復比較后的數字碼進行積分并反饋到跟蹤電容陣列上,能夠自適應跟蹤信號,解決了傳統zoom?adc容易過載的問題,增加了sar?adc的有效位數,在同樣的能量消耗情況下,能夠得到更高精度。

18、本發明提出的自適應跟蹤技術的設計實施例,能夠有效解決傳統zoom?adc精細轉換期間的超量程誤差問題,增加了sar?adc的有效位數,提高了zoom?adc的精度且電路復雜度低,降低成本。

- 還沒有人留言評論。精彩留言會獲得點贊!