一種ANPC三電平拓撲功率模塊的制作方法

本發明涉及半導體,尤其涉及一種anpc三電平拓撲功率模塊。

背景技術:

1、大功率、高頻以及高速度開關是功率模塊一個重要的發展趨勢。相比兩電平電路拓撲,三電平電路拓撲中功率芯片的電壓應力低,電壓變化率小,輸出功率更高等優點,采用多電平電路拓撲是功率模塊實現高效率大功率工作性能優勢的有效手段之一。

2、常用的多電平電路拓撲主要是三電平電路拓撲,其包括t型三電平和i型三電平電路拓撲,其中i型三電平電路拓撲又包括二極管中性點箝位型拓撲(npc,neutral?pointclamped)和有源中性點箝位型拓撲(anpc,active?neutral?point?clamped)。npc三電平拓撲通過在中性點上使用多個電容器來實現多個輸出電壓水平通過采用無源的二極管將中性點箝位在一個預定義的電壓水平上。由于器件電壓應力低,因此開關損耗小;由于無需高耐壓功率芯片,其成本相對較低;但是相比anpc拓撲模塊,npc三電平模塊具有較高的通態損耗,箝位二極管承受反向恢復電壓,存在反向回復損耗,直流母線電容充放電不平衡的問題,通常需要一個額外的直流電源來供電,以維持中性點電壓。

3、anpc三電平拓撲使用有源開關來箝位中性點電壓,而不是依賴于電容器或者無源的二極管,anpc拓撲還可以通過動態地調整中性點電壓來實現多個輸出電壓水平,從而提高了電平輸出的靈活性和優化控制性能。由于使用了額外的開關來控制或者箝位中性點電壓,anpc電路拓撲結構功率模塊通常具有更高的開關損耗和更好的動態響應。

4、相比硅igbt芯片,碳化硅mosfet芯片開關頻率高、開關損耗小。但若anpc三電平拓撲功率模塊全采用碳化硅芯片,模塊成本較大幅增加,而將碳化硅mosfet芯片和硅igbt芯片搭配使用一起整合進anpc拓撲的功率模塊成為anpc模塊降低損耗的一種非常有效的低成本手段。通過構建硅igbt和碳化硅mosfet芯片混合的anpc拓撲結構的功率模塊,再結合調制策略的優化,充分發揮碳化硅mosfet開關損耗小和硅igbt通態損耗小的優勢,優化各個器件的開關頻率及損耗分布,從而提高功率模塊的工作效率及輸出開關頻率。

5、為了充分發揮apnc電路拓撲結構的功率模塊的優異的潛力,如何基于硅igbt芯片和碳化硅mosfet芯片來搭建功率模塊的anpc電路拓撲結構是低成本開發高效率大功率模塊不得不面對的主要技術難題。

技術實現思路

1、有鑒于此,本發明的目的在于提出一種anpc三電平拓撲功率模塊,以解決如何基于硅igbt芯片和碳化硅mosfet芯片來搭建低成本、高效率大功率模塊的技術難題。

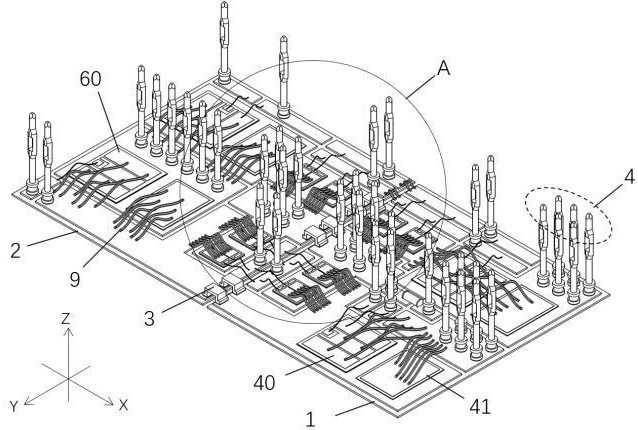

2、基于上述目的,本發明提供了一種anpc三電平拓撲功率模塊,包括:

3、絕緣板,包括第一絕緣板和第二絕緣板,所述第二絕緣板和所述第一絕緣板沿x方向并列布置在同一平面上;

4、金屬層,位于所述絕緣板的上表面,包括圖案化金屬層區域,用于實現所述功率模塊的電路拓撲結構,所述第一絕緣板和所述第二絕緣板上的金屬層之間通過金屬層連接橋電氣連接;

5、金屬針腳,包括輸入正直流母線的“dc+”針腳、輸入負直流母線的“dc-”針腳、輸出交流的“ac”針腳和中點電位箝位的“m”針腳,所述金屬針腳布置于所述金屬層上;

6、功率芯片,所述功率芯片布置于所述金屬層上,與所述金屬層電氣連接;

7、所述絕緣板、所述金屬層、所述金屬針腳和所述功率芯片連接成所述功率模塊的電路拓撲結構,所述電路拓撲結構為中性點有源箝位(anpc)的三電平拓撲結構;

8、所述三電平電路拓撲主橋臂的“dc+”針腳和“dc-”針腳沿著所述功率模塊的y方向被布局于所述模塊的右側邊,所述三電平電路拓撲箝位橋臂的中性點箝位的“m”針腳和主橋臂輸出交流的“ac”針腳沿著所述模塊的x方向被布局于所述模塊的中心區域。

9、優選的,三電平拓撲結構包括主橋臂和箝位橋臂,所述主橋臂包括四組串聯的功率芯片,其中第一組功率芯片包括第一硅igbt芯片以及與其反并聯的第一續流二極管芯片,第二組功率芯片包括并聯連接的第一碳化硅mosfet芯片和并聯連接的第二碳化硅mosfet芯片,第三組功率芯片包括并聯連接的第三碳化硅mosfet芯片和并聯連接的第四碳化硅mosfet芯片,第四組功率芯片包括第四硅igbt芯片以及與其反并聯的第四續流二極管芯片,所述箝位橋臂包括串聯的第五組功率芯片和第六組功率芯片,其中所述第五組功率芯片包括第五硅igbt芯片以及與其反并聯的第五續流二極管芯片,所述第五硅igbt芯片的集電極與所述第一硅igbt芯片的發射極和所述第二組功率芯片中的碳化硅mosfet芯片的漏極相連,所述第六組功率芯片包括第六硅igbt芯片以及與其反并聯的第六續流二極管芯片,所述第六硅igbt芯片的發射極與所述第三組功率芯片中的碳化硅mosfet的源極以及所述第四硅igbt芯片的集電極相連。

10、優選的,所述“dc+”針腳、所述“dc-”針腳、所述第一組功率芯片、所述第四組功率芯片、所述第一碳化硅mosfet芯片、所述第四碳化硅mosfet芯片和一部分所述“ac”針腳被布局在所述第一絕緣板上表面的所述金屬層上,所述第五組功率芯片、第六組功率芯片和所述第二碳化硅mosfet芯片、所述第三碳化硅mosfet芯片、所述“m”針腳和另外一部分所述“ac”針腳被布局在所述第二絕緣板上表面的所述金屬層上。

11、優選的,布局所述第二碳化硅mosfet芯片和布局所述第一碳化硅mosfet芯片的所述金屬層區域之間,以及布局所述第三碳化硅mosfet芯片和所述第四碳化硅mosfet芯片的所述金屬層區域之間均通過所述金屬層連接橋實現電氣連接。

12、優選的,布局所述第一組功率芯片的金屬層區域和布局所述第四組功率芯片的金屬層區域位于所述第一絕緣板的遠離第二絕緣板的一側,且兩金屬層區域之間被布局“dc-”針腳的金屬層區域分隔開,布局所述第一碳化硅mosfet芯片的金屬層區域和布局所述第四碳化硅mosfet芯片的金屬層區域位于所述第一絕緣板靠近第二絕緣板的半部區域且彼此緊挨,所述第四組功率芯片發射極和柵極所對應的發射極條金屬層區域和柵極條金屬層區域沿著與x方向相反的方向排列且被布局于布局所述“dc-”針腳的金屬層區域的一側。

13、優選的,布局所述第五組功率芯片的金屬層區域和布局所述第二碳化硅mosfet芯片的金屬層區域為一單一連通區域且位于所述第二絕緣板的上半部區域的上表面,布局所述第六組功率芯片的金屬層區域和布局所述第三碳化硅mosfet芯片的金屬層區域沿著x方向排列且位于所述第二絕緣板的中間區域,所述第六組功率芯片發射極對應的金屬層區域和所述第三碳化硅mosfet源極對應的金屬層區域為一單一連通區域,所述單一連通區域沿著y方向緊挨著布局所述第六組功率芯片的金屬層區域布局,且所述單一連通區域的圖案呈“⊥”形。

14、優選的,布局所述第三碳化硅mosfet芯片、布局一部分所述“ac”針腳以及所述第二碳化硅mosfet芯片源極對應的金屬層區域為一單一連通區域,所述單一連通區域呈“t”形,布局所述第四碳化硅mosfet芯片、布局另外一部分所述“ac”針腳以及所述第一碳化硅mosfet芯片源極對應的所述金屬層區域也為一成“t”形的單一連通區域,所述兩單一連通區域對稱的分布在與所述功率模塊y方向平行的中心線兩側。

15、優選的,第一碳化硅mosfet芯片柵極對應的第一柵極條金屬層區域和所述第二碳化硅mosfet芯片柵極對應的第二柵極條金屬層區域通過金屬引線實現電氣連接,所述第一碳化硅mosfet芯片源極對應的第一源極條金屬層區域和所述第二碳化硅mosfet芯片源極對應的第二源極條金屬層區域通過金屬引線實現電氣連接,所述第一柵極條金屬層區域和第一源極條金屬層區域緊挨著所述第一碳化硅mosfet芯片的金屬層區域布局。

16、優選的,第三碳化硅mosfet芯片柵極和所述第四碳化硅mosfet芯片柵極所對應的柵極條金屬層區域為同一個柵極條金屬層區域,位于所述第二絕緣板上表面,所述第三碳化硅mosfet芯片源極和所述第四碳化硅mosfet芯片源極所對應的源極條金屬層區域也為同一個源極條金屬層區域,位于所述第一絕緣板上表面,所述柵極條金屬層區域和所述源極條金屬層區域對稱的分布于與所述功率模塊y方向平行的中心線兩側。

17、優選的,第三碳化硅mosfet芯片源極對應的金屬層區域、所述第六硅igbt芯片發射極對應的金屬層區域為一單一連通區域,所述單一連通區域呈“⊥”形且沿著y方向緊挨著布局所述第六組功率芯片的金屬層區域布局;所述第四碳化硅mosfet芯片源極對應的金屬層區域、布局所述第四組功率芯片的金屬層區域為一單一連通區域,所述單一連通區域也呈“⊥”形且沿著y方向緊挨著布局所述第四碳化硅mosfet芯片的金屬層區域布局;呈“⊥”形的兩所述金屬層區域也對稱的分布于與模塊y方向平行的中心軸兩側,且相互之間通過所述金屬層連接橋實現電氣連接。

18、本發明的有益效果:本發明提出的具有有源中點箝位特征的三電平電路拓撲功率模塊,針對模塊開關時存在的因模塊寄生電感較大而產生過高電壓尖峰影響變頻器工作安全和全硅igbt功率模塊工作時損耗較大工作效率較低的問題,通過將功率模塊主功率回路對折并緊挨布局以及硅基和碳化硅基功率芯片混合的方案來降低電壓尖峰和提升變頻器工作效率,所述功率模塊可運用于高速開關和高頻領域,在新能源、工業變頻等對功率密度要求較高的大功率應用場合具有顯著的實用價值。

- 還沒有人留言評論。精彩留言會獲得點贊!