半導體結構及其制備方法與流程

本技術涉及半導體,具體地,涉及一種半導體結構及其制備方法。

背景技術:

1、cmos(complementary?metal-oxide-semiconductor,互補式金屬氧化物半導體)是一種集成電路的工藝器件,一般是在硅基晶圓模板上同時制備nmos(n-type?mosfet)和pmos(p-type?mosfet)兩種物理特性互補的基本元件。cmos因其互補特性被廣泛應用于各種電子設備與電子器件。

2、硅器件在高溫下具有豐富的本征載流子,當溫度超過300℃攝氏度時,本征載流子的數量超過摻雜載流子數量,這就意味著硅器件在長時間高溫下可能會退化或無法運行,即硅基cmos無法在高溫下正常工作;此外,高集成度的硅基cmos集成電路在工作時會產生大量的熱量,尤其是高功率半導體器件的散熱需求更高,而硅器件的特性導致其散熱性能較弱;同時,硅基cmos暴露于高劑量離子輻射或高能量γ射線場景下容易發生輻射損傷,表現為閾值電壓漂移、漏電流增加和傳輸特性退化等現象,從而降低cmos器件的性能和可靠性。

3、目前亟需一種性能穩定的互補型半導體器件。

技術實現思路

1、為了解決上述技術問題,本技術實施例中提供了一種半導體結構及其制備方法。

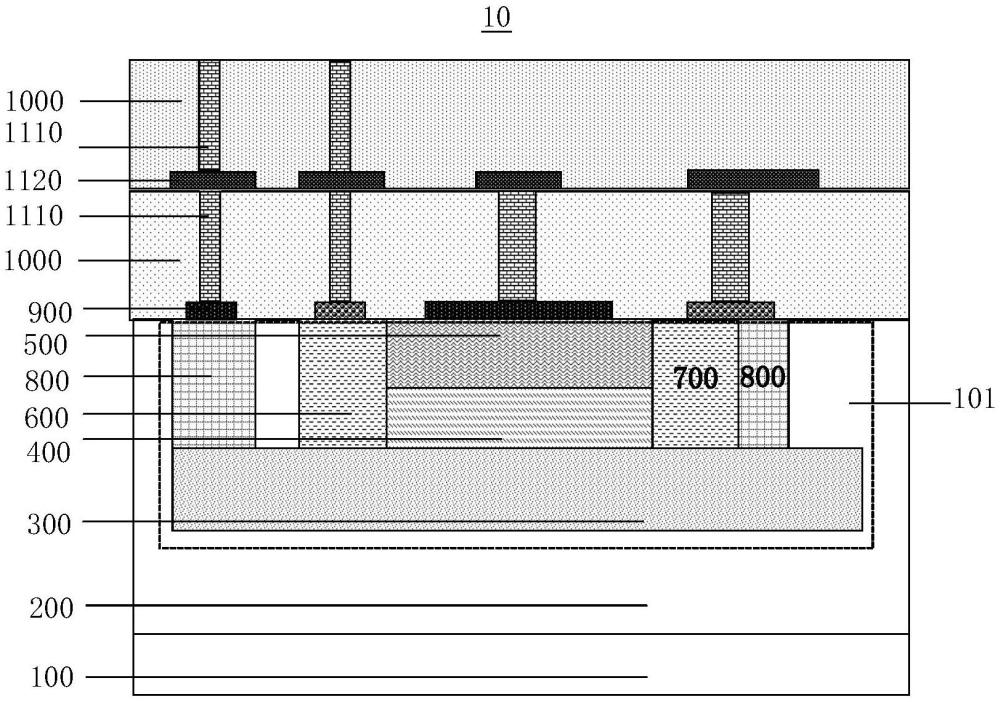

2、本技術實施例的第一個方面,提供了一種半導體結構,至少包括形成于碳化硅基體中基體單元,所述基體單元包括nfet、pfet中的至少一種,所述基體單元至少包括由外而內設置,且依次貼合的三層結構:

3、第一層結構至少包括:互相貼合的電隔離區和底柵區;

4、第二層結構設置于所述第一層結構的內部,所述第二層結構至少包括:互相電連接的漏極區、溝道區和源極區;

5、第三層結構,設置于所述第二層結構的內部,所述第三層結構至少包括:頂柵區;

6、其中,所述第一層結構與所述第二層結構之間,以及所述第二層結構與所述第三層結構之間在通電時形成pn結。

7、在本技術一個可選實施例中,所述頂柵區和所述溝道區沿垂直方向堆疊于所述底柵區表面,且所述溝道區與所述底柵區貼合;

8、所述漏極區和所述源極區分別位于所述溝道區的兩側,且均與所述頂柵區、所述溝道區和所述底柵區貼合;

9、至少兩個電隔離區,分別設置于所述漏極區和所述源極區兩側,各所述電隔離區均與所述底柵區貼合;

10、其中,所述頂柵區、所述電隔離區和所述底柵區為第一離子摻雜類型;所述漏極區、所述源極區和所述溝道區為第二離子摻雜類型;所述第一離子摻雜類型與所述第二離子摻雜類型不同。

11、在本技術一個可選實施例中,所述漏極區、所述源極區和所述溝道區為一體制成。

12、在本技術一個可選實施例中,所述基體單元包括pfet器件,所述第一離子摻雜類型為p型,所述第二離子摻雜類型為n型。

13、在本技術一個可選實施例中,所述基體單元包括nfet器件,所述第一離子摻雜類型為n型,所述第二離子摻雜類型為p型。

14、在本技術一個可選實施例中,所述碳化硅基體至少包括相互堆疊的外延層和介質層;其中,所述基體單元設置于所述外延層;

15、所述半導體結構還包括:

16、歐姆接觸層,設置于所述介質層,并分別與所述頂柵區和電連接結構電連接;所述歐姆接觸層的與所述頂柵區的離子摻雜類型相同。

17、在本技術一個可選實施例中,所述電連接結構至少包括:

18、多個填充有導電材料的層間通孔;至少一個所述層間通孔與所述歐姆接觸層電連接;

19、多個金屬互連線,與多個所述層間通孔互連,以將所述基體單元引出至器件表層。

20、在本技術一個可選實施例中,所述層間通孔為tsv鎢通孔或者tsv銅通孔。

21、在本技術一個可選實施例中,所述底柵區的離子摻雜濃度為le17/cm3~1e19/cm3;和/或,所述溝道區的離子摻雜濃度為1e17/cm3~5e19/cm3;和/或,所述頂柵區的離子摻雜濃度為1e16/cm3~1e20/cm3;和/或,所述漏極區、所述源極區的離子摻雜濃度為1e18/cm3~5e20/cm3;和/或,所述電隔離區的離子摻雜濃度1e18/cm3~5e20/cm3。

22、在本技術一個可選實施例中,所述半導體結構為cfet器件。

23、本技術實施例的第二個方面,提供了一種電子器件,包括:

24、如上任一項所述的半導體結構。

25、本技術實施例的第三個方面,提供了一種半導體結構的制備方法,至少包括:

26、在碳化硅外延層中采用局部離子注入法形成底柵區;

27、采用局部離子注入法在所述底柵區表面依次形成沿垂直方向堆疊的溝道區和頂柵區,以及相互間隔的電隔離區、漏極區和源極區;其中,所述漏極區和所述源極區分別位于所述溝道區兩側,且均與所述溝道區和所述底柵區電連接;所述電隔離區的數量為多個,且分別位于所述源極區和所述漏極區兩側;所述頂柵區、所述電隔離區和所述底柵區為第一離子摻雜類型;所述漏極區、所述源極區和所述溝道區為第二離子摻雜類型;所述第一離子摻雜類型與所述第二離子摻雜類型不同;

28、在所述外延層表面形成其他輔助結構,得到半導體結構。

29、在本技術一個可選實施例中,在形成沿垂直方向堆疊的溝道區和頂柵區,以及相互間隔的電隔離區、漏極區和源極區之后,所述方法還包括:

30、采用碳膜保護法進行雜質離子注入激活。

31、第一方面,本技術實施例提供的半導體結構為常態導通,通電自耗盡的器件結構,可以應用于任意需要常態導通的器件中,可以在一定程度上節省資源損耗;

32、第二方面,本技術實施例提供的半導體結構為碳化硅基體,硅材料的晶體結構在400℃~500℃就已經發生嚴重形變,而碳化硅在1000℃依然性能穩定,碳化硅材料在高溫下相比于硅材料的耐熱性能更為穩定,可以進一步提高半導體結構的耐高溫特性和器件可靠性;

33、第三方面,本技術實施例提供的半導體結構為碳化硅基體,碳化硅有特殊的晶體結構,聲子散射少,熱導率好,熱量很容易被導走,因此相對于傳統硅基材料的半導體結構的散熱性能更優,可以進一步提高半導體結構的散熱特性和器件可靠性;

34、第四方面,本技術實施例提供的半導體結構為碳化硅基體,碳硅鍵相對于硅硅鍵的鍵能更高,因此碳化硅材料相對于傳統的硅基材料在外界射線等輻射作用下不容易發生斷裂,不容易在基體內出現缺陷,耐輻射能力更強,可以進一步提高半導體結構的耐輻射特性和器件可靠性;

35、第五方面,本技術實施例提供的半導體結構為碳化硅基體,由于碳化硅的晶格特性,電子在碳化硅晶體中受到的阻礙相對于其他材料小,散射比較小,電子可以加速到一個很高的速度,晶格的碰撞速度高,導電性更高,在電場的作用下電子漂移速度更高,即控制信號的響應速度更高,可以將器件結構的開關速率和控制信號的頻率(或者叫器件的工作頻率)提高至一個較高的水平,提高器件結構的運行速率。

36、第六方面,本技術實施例提供的半導體結構為碳化硅基體,去除了傳統器件結構中的柵氧層,柵極區與溝道區、漏極區和源極區等均為碳化硅基體制成,為同質結器件結構,因此各區域之間不存在界面效應,大大提高載流子的遷移效率,進而獲得較高的電子或空穴的漂移速度,進一步提高半導體結構的工作效率和器件可靠性;

37、此外,漏極區、溝道區和源極區可以為一體制成,即將傳統的界面導通轉換為體導通,電子或空穴漂移速度更高,器件性能進一步提高;

38、第七方面,本技術實施例提供的半導體結構,其有源區電極均可以通過電連接結構等引出至表面,其余器件的可集成度高,封裝工藝簡單,可以進一步降低器件結構的工藝復雜度和工藝成本;

39、第八方面,本技術實施例提供的半導體結構,包含由外而內設置,且依次貼合的三層結構,第一層結構與第二層結構之間,以及第二層結構與第三層結構之間在通電時形成pn結。碳化硅禁帶足夠寬,本技術實施例采用pn結隔離把電子路徑束縛在設定的層結構內流動,避免電子散射出去而影響其他邏輯器件,對各個器件區域進行隔離,可以進一步提高器件結構的工作穩定性與可靠性。

- 還沒有人留言評論。精彩留言會獲得點贊!