一種具有MGD結構的屏蔽柵溝槽器件及其制作方法與流程

本發明屬于半導體,涉及一種具有mgd結構的屏蔽柵溝槽器件及其制作方法。

背景技術:

1、屏蔽柵溝槽(shielded?gate?trench,簡稱sgt)結構,是一種先進的mosfet技術,其采用深溝槽工藝在柵電極下方增加了屏蔽電極,與源電極相連,實現屏蔽柵極與漂移區的作用,從而減小了米勒電容和柵電荷,加快了開關速度,降低了開關損耗。

2、在一種制作sgt結構的方法中,控制柵的制備包含以下流程:氧化層刻蝕→淀積多晶硅→刻蝕多晶硅。

3、當前工藝制作的sgt結構的源漏電壓vsd較高,一般為0.7~0.8v,且反向恢復時間長,導致電路效率低下。

4、因此,如何提供一種sgt結構及其制作方法,以降低源漏電壓vsd,并降低反向恢復電荷qrr與反向恢復時間trr,提高電路效率,成為本領域技術人員亟待解決的一個重要技術問題。

技術實現思路

1、鑒于以上所述現有技術的缺點,本發明的目的在于提供一種具有mgd結構的屏蔽柵溝槽器件及其制作方法,用于解決現有屏蔽柵溝槽器件的源漏電壓vsd較高,且反向恢復時間長,導致電路效率低下的問題。

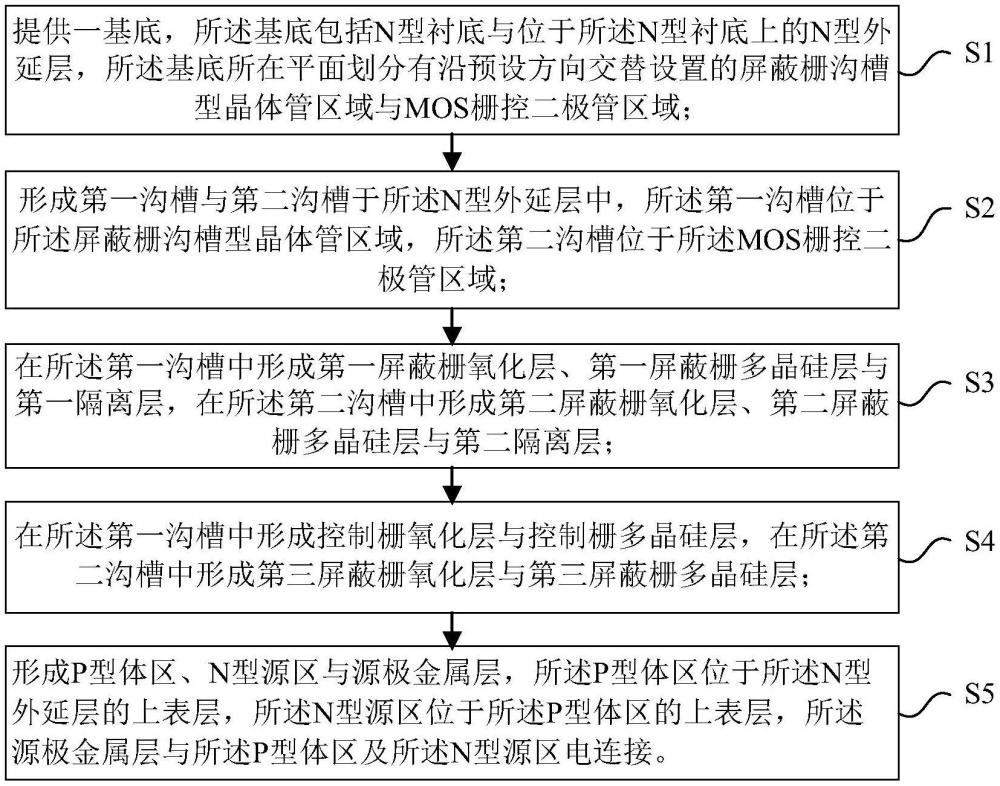

2、為實現上述目的及其他相關目的,本發明提供一種具有mgd結構的屏蔽柵溝槽器件的制作方法,包括以下步驟:

3、提供一基底,所述基底包括n型襯底與位于所述n型襯底上的n型外延層,所述基底所在平面劃分有沿預設方向交替設置的屏蔽柵溝槽型晶體管區域與mos柵控二極管區域;

4、形成第一溝槽與第二溝槽于所述n型外延層中,所述第一溝槽位于所述屏蔽柵溝槽型晶體管區域,所述第二溝槽位于所述mos柵控二極管區域;

5、在所述第一溝槽中形成第一屏蔽柵氧化層、第一屏蔽柵多晶硅層與第一隔離層,在所述第二溝槽中形成第二屏蔽柵氧化層、第二屏蔽柵多晶硅層與第二隔離層;

6、在所述第一溝槽中形成控制柵氧化層與控制柵多晶硅層,在所述第二溝槽中形成第三屏蔽柵氧化層與第三屏蔽柵多晶硅層;

7、形成p型體區、n型源區與源極金屬層,所述p型體區位于所述n型外延層的上表層,所述n型源區位于所述p型體區的上表層,所述源極金屬層與所述p型體區及所述n型源區電連接,其中,

8、所述控制柵多晶硅層位于所述第一屏蔽柵氧化層上方并與所述第一屏蔽柵氧化層之間通過所述第一隔離層相互間隔,所述第一屏蔽柵氧化層位于所述第一屏蔽柵多晶硅層的外壁與所述第一溝槽的內壁之間,所述控制柵氧化層位于所述控制柵多晶硅層的外壁與所述第一溝槽的內壁之間;

9、所述第三屏蔽柵多晶硅層位于所述第二屏蔽柵多晶硅層上方并與所述第二屏蔽柵多晶硅層之間通過所述第二隔離層間隔,所述第二屏蔽柵氧化層位于所述第二屏蔽柵多晶硅層的外壁與所述第二溝槽的內壁之間,所述第三屏蔽柵氧化層位于所述第三屏蔽柵多晶硅層的外壁與所述第二溝槽的內壁之間;

10、所述第一屏蔽柵多晶硅層、所述第二屏蔽柵多晶硅層與所述第三屏蔽柵多晶硅層均接源極電位。

11、可選地,在所述第一溝槽中形成第一屏蔽柵氧化層、第一屏蔽柵多晶硅層與第一隔離層,在所述第二溝槽中形成第二屏蔽柵氧化層、第二屏蔽柵多晶硅層與第二隔離層包括以下步驟:

12、沉積第一氧化層,所述第一氧化層覆蓋所述第一溝槽與所述第二溝槽的內壁;

13、沉積第一多晶硅層,所述第一多晶硅層填充進所述第一溝槽與所述第二溝槽中;

14、采用干法刻蝕回刻所述第一多晶硅層至第一預設深度;

15、采用濕法刻蝕腐蝕所述第一氧化層以顯露所述第一多晶硅層的部分側壁;

16、沉積第二氧化層,所述第二氧化層填充進所述第一溝槽與所述第二溝槽中并覆蓋所述第一多晶硅層的顯露表面;

17、回刻所述第二氧化層及所述第一氧化層至第二預設深度,所述第二預設深度高于所述第一預設深度,此時,所述第一氧化層位于所述第一溝槽中的部分作為所述第一屏蔽柵氧化層,所述第一氧化層位于所述第二溝槽中的部分作為所述第二屏蔽柵氧化層,所述第一多晶硅層位于所述第一溝槽中的部分作為所述第一屏蔽柵多晶硅層,所述第一多晶硅層位于所述第二溝槽中的部分作為所述第二屏蔽柵多晶硅層,所述第二氧化層位于所述第一溝槽中的部分作為所述第一隔離層,所述第二氧化層位于所述第二溝槽中的部分作為所述第二隔離層。

18、可選地,在所述第一溝槽中形成控制柵氧化層與控制柵多晶硅層,在所述第二溝槽中形成第三屏蔽柵氧化層與第三屏蔽柵多晶硅層包括以下步驟:

19、形成第三氧化層,所述第三氧化層覆蓋所述第一溝槽的顯露側壁與所述第二溝槽的顯露側壁;

20、形成光刻膠層,所述光刻膠層覆蓋于所述n型外延層上方并填充進第一溝槽與所述第二溝槽中;

21、圖形化所述光刻膠層以得到顯露所述mos柵控二極管區域的開口;

22、去除所述第三氧化層位于所述第二溝槽的側壁的部分,所述第三氧化層位于所述第一溝槽的側壁的部分作為所述控制柵氧化層;

23、去除所述光刻膠層,并形成第四氧化層,所述第四氧化層至少覆蓋所述第二溝槽的顯露側壁,所述第四氧化層覆蓋所述第二溝槽的側壁的部分作為所述第三屏蔽柵氧化層;

24、形成第二多晶硅層,所述第二多晶硅層覆蓋于所述n型外延層上方并填充進第一溝槽與所述第二溝槽中;

25、圖形化所述第二多晶硅層以得到位于所述第一溝槽中的所述控制柵多晶硅層及位于所述第二溝槽中的所述第三屏蔽柵多晶硅層。

26、可選地,一所述屏蔽柵溝槽型晶體管區域中的所述第一溝槽的數量為m,相鄰的一所述mos柵控二極管區域中的所述第二溝槽的數量為n,其中,n≥1,m≥n。

27、可選地,m/n≥5。

28、可選地,所述第三屏蔽柵氧化層的厚度小于所述控制柵氧化層的厚度。

29、可選地,所述第三屏蔽柵氧化層的厚度范圍是60埃~70埃,所述控制柵氧化層的厚度范圍是250埃~350埃。

30、本發明還提供一種具有mgd結構的屏蔽柵溝槽器件,包括:

31、基底,包括n型襯底與位于所述n型襯底上的n型外延層,所述基底所在平面劃分有沿預設方向交替設置的屏蔽柵溝槽型晶體管區域與mos柵控二極管區域;

32、第一溝槽與第二溝槽,位于所述n型外延層中,所述第一溝槽位于所述屏蔽柵溝槽型晶體管區域,所述第二溝槽位于所述mos柵控二極管區域;

33、第一屏蔽柵氧化層、第一屏蔽柵多晶硅層、第一隔離層、控制柵氧化層與控制柵多晶硅層,位于所述第一溝槽中,所述控制柵多晶硅層位于所述第一屏蔽柵氧化層上方并與所述第一屏蔽柵氧化層之間通過所述第一隔離層相互間隔,所述第一屏蔽柵氧化層位于所述第一屏蔽柵多晶硅層的外壁與所述第一溝槽的內壁之間,所述控制柵氧化層位于所述控制柵多晶硅層的外壁與所述第一溝槽的內壁之間,所述第一屏蔽柵多晶硅層接源極電位;

34、第二屏蔽柵氧化層、第二屏蔽柵多晶硅層、第二隔離層、第三屏蔽柵氧化層與第三屏蔽柵多晶硅層,位于所述第二溝槽中,所述第三屏蔽柵多晶硅層位于所述第二屏蔽柵多晶硅層上方并與所述第二屏蔽柵多晶硅層之間通過所述第二隔離層間隔,所述第二屏蔽柵氧化層位于所述第二屏蔽柵多晶硅層的外壁與所述第二溝槽的內壁之間,所述第三屏蔽柵氧化層位于所述第三屏蔽柵多晶硅層的外壁與所述第二溝槽的內壁之間,所述第二屏蔽柵多晶硅層與所述第三屏蔽柵多晶硅層均接源極電位;

35、p型體區、n型源區與源極金屬層,所述p型體區位于所述n型外延層的上表層,所述n型源區位于所述p型體區的上表層,所述源極金屬層與所述p型體區及所述n型源區電連接。

36、可選地,一所述屏蔽柵溝槽型晶體管區域中的所述第一溝槽的數量為m,相鄰的一所述mos柵控二極管區域中的所述第二溝槽的數量為n,其中,n≥1,m≥n。

37、可選地,m/n≥5。

38、可選地,所述第三屏蔽柵氧化層的厚度小于所述控制柵氧化層的厚度。

39、可選地,所述第三屏蔽柵氧化層的厚度范圍是60埃~70埃,所述控制柵氧化層的厚度范圍是250埃~350埃。

40、如上所述,本發明的具有mgd結構的屏蔽柵溝槽器件及其制作方法在普通sgt器件中集成了mgd結構,其中,基底所在平面劃分有沿預設方向交替設置的屏蔽柵溝槽型晶體管區域與mos柵控二極管區域,屏蔽柵溝槽型晶體管區域與mos柵控二極管區域分別設有第一溝槽與第二溝槽,mgd結構包括位于第二溝槽中的第二屏蔽柵氧化層、第二屏蔽柵多晶硅層、第二隔離層、第三屏蔽柵氧化層與第三屏蔽柵多晶硅層,第三屏蔽柵多晶硅層位于第二屏蔽柵多晶硅層上方并與第二屏蔽柵多晶硅層之間通過第二隔離層間隔,第二屏蔽柵多晶硅層與第三屏蔽柵多晶硅層均接源極電位。本發明通過在器件中增設mgd結構來降低器件源漏電壓vsd,同時能夠降低反向恢復電荷qrr與反向恢復時間trr,從而提高電路效率,其中,在器件關斷的時候,電路提供抽取電流,將反向恢復電荷qrr從外延層中抽取至mgd結構的上層多晶硅層排出。

- 還沒有人留言評論。精彩留言會獲得點贊!