一種測試電路及存儲器的制作方法

本公開涉及半導體存儲器,尤其涉及一種測試電路及存儲器。

背景技術:

1、動態隨機存取存儲器(dynamic?random?access?memory,dram)作為一種半導體存儲器,尤其是第5代ddr(5th?double?data?rate,ddr5),因具有高效能和低成本的特性被廣泛應用在各種電子產品上。目前存儲器最常用的測試方法是存儲器內建自測試(memorybuild?in?self?test,mbist)方法,mbist電路以存儲器為目標,自動生成存儲器的測試電路,通過執行特定的測試算法,來檢測存儲器中存在的某些缺陷。

技術實現思路

1、本公開提供了一種測試電路及存儲器。

2、本公開的技術方案是這樣實現的:

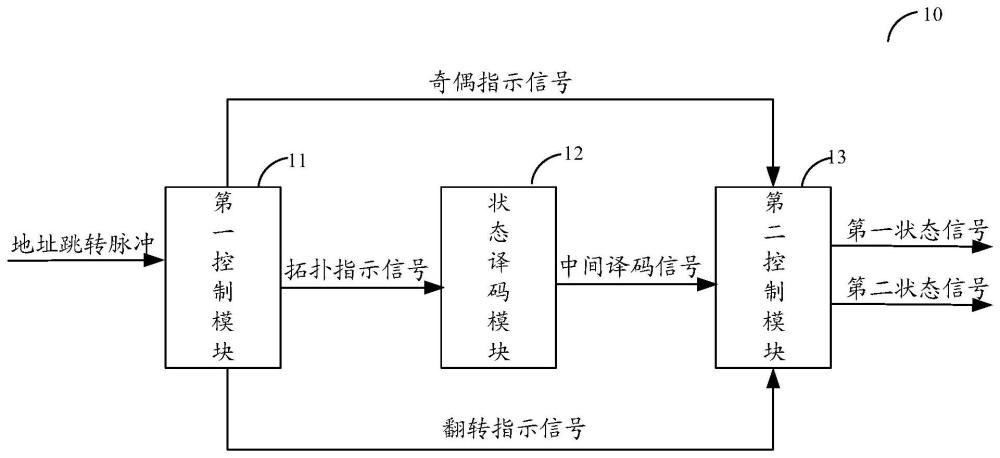

3、第一方面,本公開實施例提供了一種測試電路,所述測試電路利用多個預設數據拓撲對存儲陣列進行讀寫測試;所述測試電路包括:

4、第一控制模塊,配置為基于接收到的地址跳轉脈沖,產生并輸出奇偶指示信號、翻轉指示信號和拓撲指示信號;其中,所述地址跳轉脈沖指示已執行目標操作的行地址的計數值達到偶數最高位或奇數最高位,所述目標操作是指讀操作或寫操作;

5、狀態譯碼模塊,與所述第一控制模塊連接,配置為對所述拓撲指示信號進行計數和譯碼,得到中間譯碼信號;

6、第二控制模塊,與所述第一控制模塊和所述狀態譯碼模塊連接,配置為基于所述奇偶指示信號、所述翻轉指示信號和所述中間譯碼信號,生成并輸出第一狀態信號和第二狀態信號;

7、其中,所述第一狀態信號用于將第一數據序列和第二數據序列的兩者之一選中為目標數據序列,所述第二狀態信號指示所述目標數據序列的每一數據是否翻轉,所述目標數據序列或翻轉后的所述目標數據序列用于構成所述預設數據拓撲。

8、在一些實施例中,所述預設數據拓撲具有a組,每一組所述預設數據拓撲包括第一數據拓撲和第二數據拓撲,每一個所述第一數據拓撲和所述第二數據拓撲均包括奇數據拓撲和偶數據拓撲;

9、所述奇偶指示信號指示執行所述目標操作對應的存儲單元的行地址為奇數行地址或偶數行地址,并生成對應的所述奇數據拓撲或所述偶數據拓撲;

10、所述拓撲指示信號指示執行所述目標操作對應的所述預設數據拓撲的組編號;所述翻轉指示信號指示執行所述目標操作對應的所述第一數據拓撲或所述第二數據拓撲。

11、在一些實施例中,所述第一控制模塊,還配置為基于接收到所述地址跳轉脈沖,產生并輸出讀寫指示信號;其中,所述讀寫指示信號指示讀操作或寫操作。

12、在一些實施例中,所述測試電路還包括測試模塊;

13、所述測試模塊,與所述第一控制模塊和所述第二控制模塊均連接,配置為接收所述讀寫指示信號、所述第一狀態信號和所述第二狀態信號;在所述讀寫指示信號指示寫操作時,基于所述第一狀態信號和所述第二狀態信號向所述存儲陣列寫入對應的所述預設數據拓撲;或者,在所述讀寫指示信號指示讀操作時,讀取所述存儲陣列的數據,并基于所述第一狀態信號和所述第二狀態信號對讀取到的數據進行比對處理。

14、在一些實施例中,所述第一控制模塊,具體配置為每接收到1個所述地址跳轉脈沖,控制所述奇偶指示信號的電平狀態發生一次翻轉;每接收到2個所述地址跳轉脈沖,控制所述讀寫指示信號的電平狀態發生一次翻轉,每接收到4個所述地址跳轉脈沖,控制所述翻轉指示信號的電平狀態發生一次翻轉,每接收到8個所述地址跳轉脈沖,產生1個所述拓撲指示信號。

15、在一些實施例中,所述第一控制模塊包括:

16、第一信號單元,配置為利用所述地址跳轉脈沖對所述奇偶指示信號的反相信號進行采樣處理,產生新的所述奇偶指示信號;

17、第二信號單元,與所述第一信號單元連接,配置為對所述奇偶指示信號和所述讀寫指示信號進行邏輯處理產生第一中間信號;以及,基于所述地址跳轉脈沖對所述第一中間信號進行采樣,產生新的所述讀寫指示信號;

18、第三信號單元,與所述第二信號單元連接,配置為對所述奇偶指示信號、所述讀寫指示信號和所述翻轉指示信號進行邏輯處理產生第二中間信號;以及,基于所述地址跳轉脈沖對所述第二中間信號進行采樣,產生新的所述翻轉指示信號;

19、第四信號單元,與所述第三信號單元連接,配置為對所述奇偶指示信號、所述讀寫指示信號和所述翻轉指示信號進行邏輯處理得到第三中間信號;基于所述第三中間信號、所述地址跳轉脈沖和預設系統時鐘信號,產生所述拓撲指示信號。

20、在一些實施例中,所述狀態譯碼模塊包括計數單元和c個譯碼單元,所述中間譯碼信號的數量為c個;

21、所述計數單元,與所述第一控制模塊連接,配置為對所述拓撲指示信號的脈沖進行計數,產生第一計數值;

22、第j個所述譯碼單元,與所述計數單元連接,配置為在所述第一計數值符合第j個譯碼條件時,控制第j個所述中間譯碼信號處于第一狀態;在所述第一計數值不符合第j個譯碼條件時,控制第j個所述中間譯碼信號處于第二狀態;其中,j為大于等于1且小于等于c的整數;c≤a;所述第一計數值包括b位子參數,2b≥a。

23、在一些實施例中,所述第二控制模塊包括:

24、第一邏輯單元,配置為對c個所述中間譯碼信號進行邏輯處理,輸出第一狀態偶信號、第一狀態奇信號、第二狀態偶信號和第二狀態奇信號;

25、第二邏輯單元,配置為基于所述奇偶指示信號,將所述第一狀態偶信號和所述第一狀態奇信號的二者之一輸出為第一預選信號;以及,基于所述奇偶指示信號將所述第二狀態偶信號和所述第二狀態奇信號的二者之一輸出為第二預選信號;

26、輸出單元,配置為將所述第一預選信號輸出為所述第一狀態信號;以及,基于所述翻轉指示信號,將所述第二預選信號和所述第二預選信號的反相信號的二者之一輸出為所述第二狀態信號。

27、在一些實施例中,所述第一邏輯單元包括:

28、預處理單元,配置為對c個所述中間譯碼信號進行邏輯處理,輸出第一選擇偶信號、第一選擇奇信號、第二選擇偶信號和第二選擇奇信號;

29、選擇單元,配置為基于所述第一選擇偶信號,將標準0信號和標準1信號的二者之一輸出為所述第一狀態偶信號;

30、基于所述第一選擇奇信號,將標準0信號和標準1信號的二者之一輸出為所述第一狀態奇信號;

31、基于所述第二選擇偶信號,將標準0信號和標準1信號的二者之一輸出為所述第二狀態偶信號;

32、基于所述第二選擇奇信號,將標準0信號和標準1信號的二者之一輸出為所述第二狀態奇信號。

33、在一些實施例中,所述第一信號單元包括第一觸發器:所述第一觸發器的時鐘端接收所述地址跳轉脈沖,所述第一觸發器的輸入端與其反相輸出端連接,所述第一觸發器的正相輸出端輸出所述奇偶指示信號;

34、所述第二信號單元包括第一異或門和第二觸發器;所述第一異或門的第一輸入端接收所述奇偶指示信號,所述第一異或門的第二輸入端與所述第二觸發器的正相輸出端連接,所述第一異或門的輸出端輸出所述第一中間信號,所述第二觸發器的輸入端接收所述第一中間信號,所述第二觸發器的時鐘端接收所述地址跳轉脈沖,所述第二觸發器的正相輸出端輸出所述讀寫指示信號;

35、所述第三信號單元包括第一與門、第二異或門和第三觸發器;所述第一與門的第一輸入端接收所述讀寫指示信號,所述第一與門的第二輸入端接收所述奇偶指示信號,所述第一與門的輸出端與所述第二異或門的第一輸入端連接,所述第二異或門的第二輸入端與所述第三觸發器的正相輸出端連接,所述第二異或門的輸出端輸出所述第二中間信號,所述第三觸發器的輸入端接收所述第二中間信號,所述第三觸發器的時鐘端接收所述地址跳轉脈沖,所述第三觸發器的正相輸出端輸出所述翻轉指示信號;

36、所述第四信號單元包括第二與門、第三異或門、第四觸發器、第五觸發器和第四異或門;所述第二與門的第一輸入端與所述第一與門的輸出端連接,所述第二與門的第二輸入端接收所述翻轉指示信號,所述第二與門的輸出端與所述第三異或門的第一輸入端連接,所述第三異或門的第二輸入端與所述第四觸發器的正相輸出端連接,所述第三異或門的輸出端輸出所述第三中間信號,所述第四觸發器的輸入端接收所述第三中間信號,所述第四觸發器的時鐘端接收所述地址跳轉脈沖,所述第四觸發器的正相輸出端與所述第五觸發器的輸入端連接,所述第五觸發器的時鐘端接收所述預設系統時鐘信號,所述第五觸發器的正相輸出端與所述第四異或門的第一輸入端連接,所述第四異或門的第二輸入端與所述第四觸發器的正相輸出端連接,所述第四異或門的輸出端輸出所述拓撲指示信號。

37、在一些實施例中,在2a=12的情況下,b=3,c=5;

38、相應的,所述計數單元包括第六觸發器、第五異或門、第七觸發器、第三與門、第六異或門和第八觸發器;

39、所述第六觸發器、所述第七觸發器和所述第八觸發器的時鐘端接收所述拓撲指示信號,所述第六觸發器的輸入端與其反相輸出端連接,所述第六觸發器的正相輸出端與所述第五異或門的第一輸入端連接,所述第五異或門的第二輸入端與所述第七觸發器的正相輸出端連接,所述第五異或門的輸出端與所述第七觸發器的輸入端連接,所述第七觸發器的正相輸出端與所述第三與門的第一輸入端連接,所述第三與門的第二輸入端與所述第六觸發器的正相輸出端連接,所述第三與門的輸出端輸出與所述第六異或門的第一輸入端連接,所述第六異或門的第二輸入端與所述第八觸發器的正相輸出端連接,所述第六異或門的輸出端與所述第八觸發器的輸入端連接;所述第六觸發器的正相輸出端輸出所述第一計數值的第1位子參數,所述第七觸發器的正相輸出端輸出所述第一計數值的第2位子參數,所述第八觸發器的正相輸出端輸出所述第一計數值的第3位子參數。

40、在一些實施例中,所述預處理單元包括第一邏輯器、第二邏輯器、第三邏輯器和第四邏輯器;

41、所述第一邏輯器的輸入端接收c個所述中間譯碼信號的部分信號,所述第一邏輯器的輸出端輸出所述第一選擇偶信號;

42、所述第二邏輯器的輸入端接收c個所述中間譯碼信號的部分信號,所述第二邏輯器的輸出端輸出所述第一選擇奇信號;

43、所述第三邏輯器的輸入端接收c個所述中間譯碼信號的部分信號,所述第三邏輯器的輸出端輸出所述第二選擇偶信號;

44、所述第四邏輯器的輸入端接收c個所述中間譯碼信號的部分信號,所述第四邏輯器的輸出端輸出所述第二選擇奇信號;

45、其中,當所述中間譯碼信號不同時,所述第一選擇偶信號、所述第一選擇奇信號、所述第二選擇偶信號和所述第二選擇偶信號不完全相同。

46、在一些實施例中,所述選擇單元包括第一選擇器、第二選擇器、第三選擇器和第四選擇器;

47、所述第一選擇器的第一輸入端接收所述標準1信號,所述第一選擇器的第二輸入端接收所述標準0信號,所述第一選擇器的控制端接收所述第一選擇偶信號,所述第一選擇器的輸出端輸出所述第一狀態偶信號;

48、所述第二選擇器的第一輸入端接收所述標準1信號,所述第二選擇器的第二輸入端接收所述標準0信號,所述第二選擇器的控制端接收所述第一選擇奇信號,所述第二選擇器的輸出端輸出所述第一狀態奇信號;

49、所述第三選擇器的第一輸入端接收所述標準0信號,所述第一選擇器的第二輸入端接收所述標準1信號,所述第三選擇器的控制端接收所述第二選擇偶信號,所述第三選擇器的輸出端輸出所述第二狀態偶信號;

50、所述第四選擇器的第一輸入端接收所述標準0信號,所述第四選擇器的第二輸入端接收所述標準1信號,所述第四選擇器的控制端接收所述第二選擇奇信號,所述第四選擇器的輸出端輸出所述第二狀態奇信號。

51、在一些實施例中,

52、所述第二邏輯單元包括第五選擇器和第六選擇器;所述第五選擇器的第一輸入端接收所述第一狀態偶信號,所述第五選擇器的第二輸入端接收所述第一狀態奇信號,所述第五選擇器的控制端接收所述奇偶指示信號,所述第五選擇器的輸出端輸出所述第一預選信號;所述第六選擇器的第一輸入端接收所述第二狀態偶信號,所述第六選擇器的第二輸入端接收所述第二狀態奇信號,所述第六選擇器的控制端接收所述奇偶指示信號,所述第六選擇器的輸出端輸出所述第二預選信號;

53、所述輸出單元包括緩沖器、第三非門和第七選擇器;所述緩沖器的輸入端接收所述第一預選信號,所述緩沖器的輸出端輸出所述第一狀態信號;所述第三非門的輸入端接收所述第二預選信號,所述第三非門的輸出端與所述第七選擇器的第一輸入端連接,所述第七選擇器的第二輸入端接收所述第二預選信號,所述第七選擇器的控制端接收所述翻轉指示信號,所述第七選擇器的輸出端輸出所述第二狀態信號。

54、在一些實施例中,所述第一觸發器至所述第八觸發器所有的復位端均接收啟動信號;其中,若所述啟動信號指示所述測試電路開始工作,則所述第一觸發器至所述第八觸發器均執行復位操作。

55、第二方面,本公開實施例提供了一種存儲器,該存儲器包括如第一方面任一項所述的測試電路。

56、本公開實施例提供了一種測試電路及存儲器,該測試電路能夠在接收到地址跳轉脈沖、奇偶指示信號、翻轉指示信號和拓撲指示信號后能夠自動完成預設數據拓撲的讀寫操作;而且,該測試電路可以在奇數或偶數計數達到最高位時改變輸入數據,在地址遍歷完改變讀寫狀態,在做完一個預設數據拓撲的測試后通過翻轉測試數據實現另一個預設數據拓撲的測試,循環控制,直至所有的預設數據拓撲測試完。

- 還沒有人留言評論。精彩留言會獲得點贊!