一種整合異構處理器共享內存的芯片架構、芯片及其設計方法與流程

本發明涉及半導體集成電路領域,尤其涉及一種整合異構處理器共享內存的芯片架構、芯片及其設計方法。

背景技術:

1、隨著科技的發展,人工智能的應用越來越廣泛,而人工智能大模型的訓練需要大量的內存空間和高效的數據處理能力,因此,芯片設計架構在人工智能領域的重要性日益凸顯,即設計一種既能夠滿足大量內存空間需求,同時又降低內存訪問時延的芯片架構成為一個重要的研究方向。

2、此外,微電子封裝技術和高速網絡通信設備也是影響芯片性能的重要因素,即芯片設計架構、微電子封裝技術和高速網絡通信設備的設計和制造水平直接影響到產品的性能和成本。

3、現有的芯片設計架構主要是以中央處理單元(cpu)為核心,通過總線結構連接各個功能模塊。這種架構在一定程度上可以滿足基本的計算需求,但是隨著人工智能大模型的出現,對內存空間和數據處理能力的需求越來越大,現有的芯片設計架構已經越來越無法滿足這些需求。

4、此外,現有的芯片設計架構在面對大規模的數據處理和內存訪問時,存在時延高、能耗大、設計和制造成本高的問題。

5、以上背景技術內容的公開僅用于輔助理解本技術的構思及技術方案,其并不必然屬于本技術的現有技術,也不必然會給出技術教導;在沒有明確的證據表明上述內容在本技術的申請日之前已經公開的情況下,上述背景技術不應當用于評價本技術的新穎性和創造性。

技術實現思路

1、本發明的目的是提供一種改進的芯片架構,除專屬近端內存之外,處理器能夠共享訪問中間級內存或遠端內存,以支持大模型運算所需的內存空間。

2、為達到上述目的,本發明采用的技術方案如下:

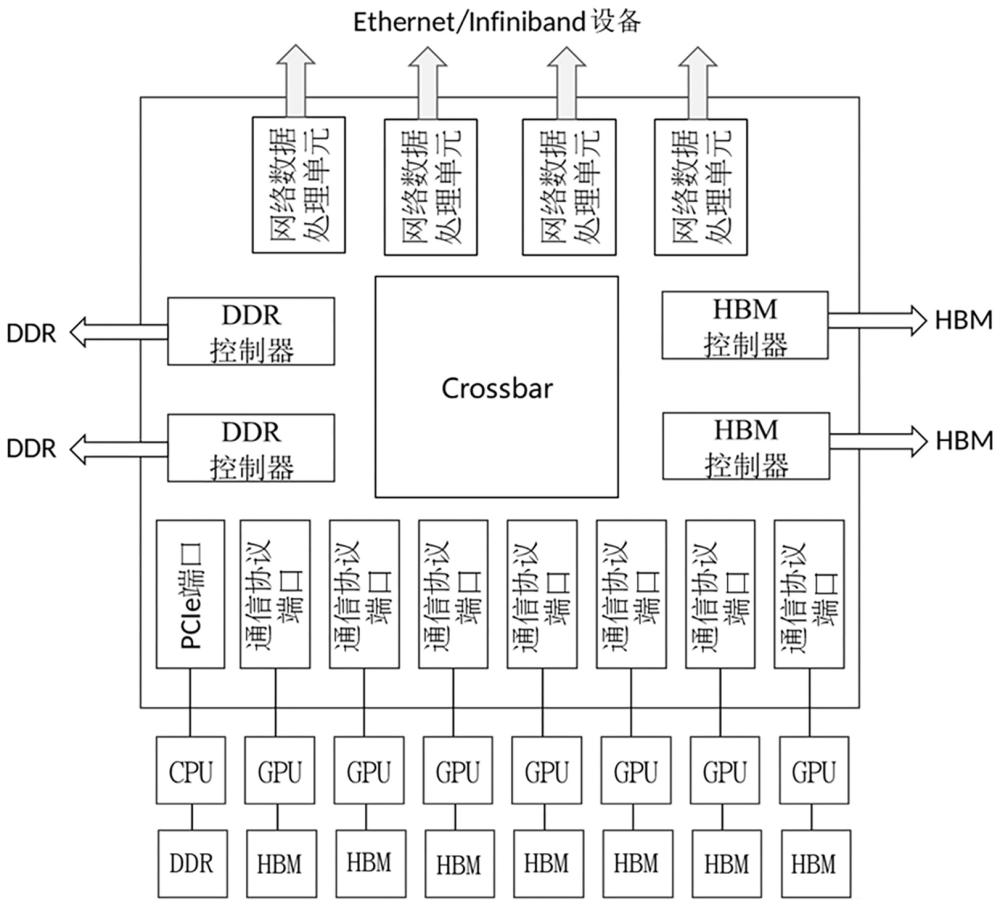

3、一種整合異構處理器共享內存的芯片架構,包括cpu、gpu、內存單元及基于crossbar結構布設的多個處理器端口、一個或多個內存處理單元和網絡數據處理單元,所述處理器端口、內存處理單元、網絡數據處理單元之間通過crossbar結構作數據交換;

4、其中,cpu、gpu與對應的處理器端口連接;

5、所述內存單元包括近端內存、中間級內存和遠端內存,其中,所述近端內存與cpu、gpu連接,所述中間級內存與對應的內存處理單元連接,所述遠端內存設置在網絡設備上并與對應的網絡數據處理單元連接;

6、所述cpu和gpu均被配置為能夠通過所述crossbar結構訪問所述中間級內存和遠端內存。

7、進一步地,承前所述的任一技術方案或多個技術方案的組合,根據crossbar結構的多端口結構調節處理器端口、內存處理單元和網絡數據處理單元的數量分配。

8、進一步地,承前所述的任一技術方案或多個技術方案的組合,所述處理器端口包括至少一個pcie端口和多個通信協議端口,其中,所述pcie端口對接cpu,所述通信協議端口與gpu一一對應連接。

9、進一步地,承前所述的任一技術方案或多個技術方案的組合,所述近端內存包括近端ddr內存和近端hbm內存,其中,所述近端ddr內存與cpu連接,所述近端hbm內存與gpu一一對應連接。

10、進一步地,承前所述的任一技術方案或多個技術方案的組合,所述中間級內存包括中間級ddr內存和中間級hbm內存,部分內存處理單元與所述中間級ddr內存連接,其余部分內存處理單元與所述中間級hbm內存連接。

11、進一步地,承前所述的任一技術方案或多個技術方案的組合,所述內存處理單元包括一個或多個ddr控制器及一個或多個hbm控制器,其中,所述ddr控制器與所述中間級ddr內存連接,所述hbm控制器與所述中間級hbm內存連接。

12、進一步地,承前所述的任一技術方案或多個技術方案的組合,所述ddr控制器通過pcie總線與所述中間級ddr內存連接,所述hbm控制器通過通信協議總線與所述中間級hbm內存連接。

13、進一步地,承前所述的任一技術方案或多個技術方案的組合,根據所述網絡數據處理單元的網絡通信方式將所述遠端內存配置在ethernet設備上或infiniband設備上。

14、根據本發明的另一方面,提供了一種整合異構處理器共享內存的芯片,包括基于crossbar結構布設的多個處理器端口、一個或多個內存處理單元和網絡數據處理單元,所述處理器端口、內存處理單元、網絡數據處理單元之間通過crossbar結構作數據交換;

15、所述處理器端口被配置為分別與cpu、gpu連接;

16、所述內存處理單元被配置為與中間級內存連接;

17、所述網絡數據處理單元被配置為與網絡設備連接;

18、所述cpu和gpu均被配置為能夠通過所述crossbar結構訪問所述中間級內存。

19、進一步地,承前所述的任一技術方案或多個技術方案的組合,與所述網絡數據處理單元連接的所述網絡設備配置有遠端內存;

20、所述cpu和gpu均被配置為能夠通過所述crossbar結構訪問所述遠端內存。

21、根據本發明的再一方面,提供了一種整合處理器共享內存的芯片架構設計方法,包括以下步驟:

22、構建crossbar作為數據交換中心,使處理器端口與內存處理單元通過crossbar能夠作數據交互;

23、將所述處理器端口與處理器連接,將所述內存處理單元與中間級內存連接;

24、配置所述處理器以能夠通過crossbar訪問所述中間級內存。

25、進一步地,承前所述的任一技術方案或多個技術方案的組合,本發明提供的芯片架構設計方法還包括:

26、增加網絡數據處理單元,使其通過crossbar能夠與處理器端口、內存處理單元作數據交互;

27、將網絡數據處理單元與網絡設備連接,其中,所述網絡設備配置有遠端內存;

28、配置所述處理器以能夠通過crossbar訪問所述遠端內存。

29、進一步地,承前所述的任一技術方案或多個技術方案的組合,本發明提供的芯片架構設計方法還包括:

30、設計所述處理器為包括cpu和gpu的異構處理器;

31、配置所述處理器端口的數量為復數個,以與一個或多個cpu和gpu一一對應連接;

32、且配置與所述cpu和gpu一一對應的近端內存;

33、當所述近端內存小于當前內存空間需求時,對應的處理器向crossbar發送訪問中間級內存和/或遠端內存的請求。

34、本發明提供的技術方案帶來的有益效果如下:

35、a.?提供一種簡潔、易于實現的以數據交換功能為中心的芯片設計架構,該架構利用多端口的crossbar結構,提供極低時延的數據交換,保障數據交換的流暢性,大大降低了異構處理器在運算時內存訪問的時延;

36、b.?整合擴展分享內存的功能:芯片架構中除專屬近端內存之外,處理器能夠共享訪問中間級內存或遠端內存,以支持大模型運算所需的內存空間;

37、c.?提供一種改進的芯片架構,適用于異構處理器,改變傳統的以cpu為核心的架構,而是演變為以算力為主的gpu處理器,適應大規模數據處理的計算,保證整體系統的穩定性;

38、d.?以system?on?chip的理念,將芯片架構微縮至高密度的系統級芯片,對于功耗敏感的系統設備來說,具有重要的實用價值:單一封裝結構下可以控制數據交換的時延,降低人工智能運算中心內大量運算所衍生的高功耗所形成的營運成本,同時也有利于提高系統的性能和穩定性。

- 還沒有人留言評論。精彩留言會獲得點贊!