多BANK時鐘偏移調節電路及FPGA芯片的制作方法

本發明涉及集成電路時鐘設計,特別是涉及一種多bank時鐘偏移調節電路及fpga(field?programmable?gate?array,現場可編程邏輯門陣列)芯片。

背景技術:

1、可編程輸入/輸出(input/output,io)單元是fpga芯片與外界電路的接口部分,能夠完成不同電氣特性下對信號的驅動與匹配要求。為了便于管理與適應各種電器標準,通常將io單元中的io端口進行邏輯和物理上的分區,將其劃分為多bank。每個bank可以獨立配置電壓和端口標準,且不同的bank可以同時執行不同的信號處理任務,因此有助于提高設計靈活性和信號完整性。

2、在有些高速應用的情況下,fpga在實現一些特定功能時可能需要多bank組合使用,因此會產生多bank的時鐘收斂問題。傳統方案通常是基于fpga自身的時鐘結構去平衡不同bank的時鐘信號,但是由于fpga內部的時鐘結構承載了大量非常靈活的時鐘選擇電路,不僅傳輸距離較遠,導致時鐘延遲較高,而且還會占用fpga自身的時鐘管理資源,提高了時鐘對齊電路的設計與調試難度,因此難以有效控制時鐘信號偏移。

技術實現思路

1、本發明要解決的技術問題是:采用fpga自身時鐘結構實現bank時鐘收斂的傳統方法存在時鐘信號傳輸距離較遠且占用大量fpga自身時鐘管理資源,導致難以有效控制時鐘信號偏移的問題。

2、為了解決上述技術問題,本發明實施例提供了一種多bank時鐘偏移調節電路及fpga芯片。

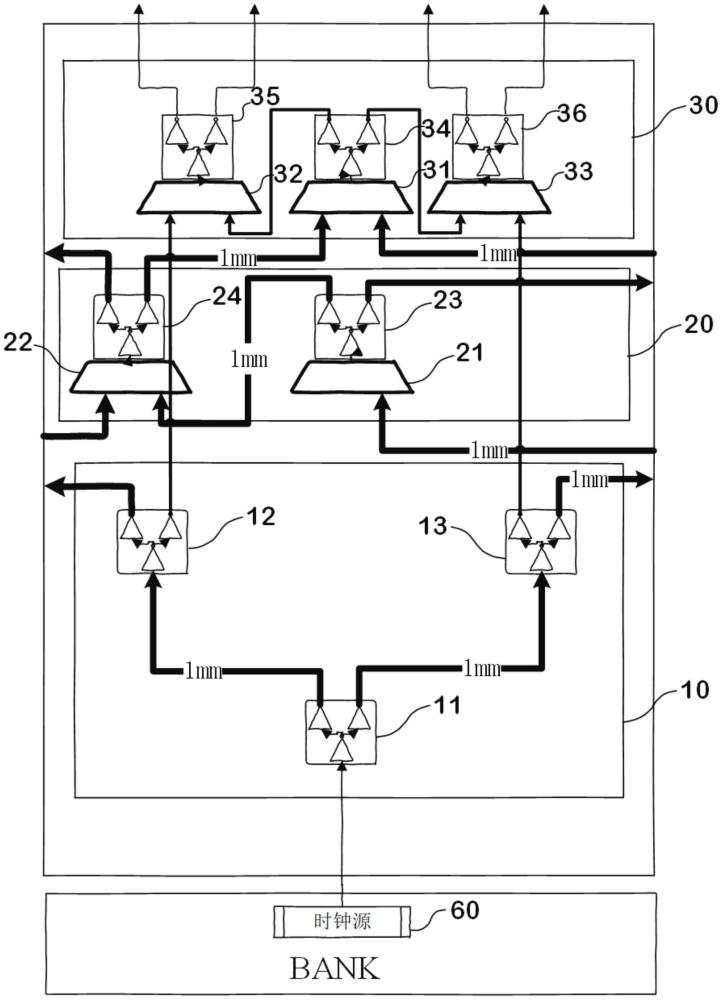

3、第一方面,本發明實施例提出的一種多bank時鐘偏移調節電路包括若干個級聯的時鐘樹,每個所述時鐘樹的根節點對應連接一bank的時鐘源信號,每個所述時鐘樹的末端葉節點作為偏移調節后的時鐘信號輸出端;

4、每個所述時鐘樹包括多個緩沖器和多個數據選擇器,以便基于同一個時鐘源信號,構建若干個長度相等的信號傳輸路徑,其中,每個所述信號傳輸路徑由至少兩個相鄰的時鐘樹中的部分緩沖器和部分數據選擇器參與構建,所述信號傳輸路徑的起點連接所述時鐘源信號,所述信號傳輸路徑的終點為參與構建所述信號傳輸路徑的任意一個時鐘樹的末端葉節點。

5、本發明實施例對應每一bank分別設置一個時鐘樹,并將相鄰bank對應的時鐘偏移調節電路級聯,從而在多bank之間建立若干個長度相等的信號傳輸路徑。在需要多個bank組合使用的情況下,多個bank能夠使用同一時鐘源發出的時鐘信號,并經上述長度相等的信號傳輸路徑達到各個bank對應的io端口,使得同一時鐘源信號在不同bank對應的時鐘樹之間傳輸時具有一致的延遲特性,減少了由于信號傳輸路徑長度差異引起的時鐘偏差,實現多bank組合使用時的時鐘對齊收斂。

6、相比現有的時鐘對齊方法,因為本發明實施例不依靠fpga自身的時鐘結構去平衡不同bank之間的時鐘源信號,因此無需將時鐘源信號先傳輸到fpga自身的時鐘結構,再傳輸到不同bank對應的io端口,而是直接將同一時鐘源信號經各個bank對應設置的所述信號傳輸路徑傳輸到對應io端口,縮短了時鐘源信號的傳輸距離,更有利于減低時鐘源信號延遲。此外,本發明實施例在各個bank的時鐘源處設置上述時鐘偏移調節電路,不會占用fpga自身的時鐘管理資源即可實現不同bank之間的時鐘偏移調節。由此可見,本發明實施例提出的上述多bank時鐘偏移調節電路具有節省fpga時鐘管理資源、降低時鐘延遲的優點,能夠提高多bank之間的時鐘偏移調節效果,降低了多bank之間時鐘對齊電路的設計與調試難度。

7、可選的,在本發明的一些實施例中,所述時鐘源信號在每個所述信號傳輸路徑上經過的緩沖器數量和數據選擇器數量分別相等,且所述緩沖器之間以及所述緩沖器與所述數據選擇器之間的走線總長度相等。

8、在本發明實施例中,所述信號傳輸路徑的長度相等表現兩個方面,分別為信號傳輸路徑上的元器件數量相等以及走線長度相等,通過設置各個緩沖器和數據選擇器的電路連接結構,能夠有效控制同一時鐘源經各個信號傳輸路徑到達不同io端口的時鐘偏移,從而提高多bank之間時鐘源信號的同步性。

9、可選的,在本發明的一些實施例中,所述緩沖器包括一個輸入端和兩個輸出端。

10、在本發明實施例中提出的所述多bank時鐘偏移調節電路中,通過模擬方法設計具有兩個輸出端的緩沖器,實現信號傳輸路徑的分支的同時,提高了緩沖器對時鐘源信號的驅動能力,進而提高上述信號傳輸路徑的信號傳輸能力,確保時鐘源信號在上述信號傳輸路徑上的強度與完整性。

11、可選的,在本發明的一些實施例中,在四bank組合使用的情況下,每個所述時鐘樹包括:

12、第一路徑選擇單元、第二路徑選擇單元以及第三路徑選擇單元;

13、其中,所述第一路徑選擇單元的輸入端連接所述時鐘源信號,所述第一路徑選擇單元的第一輸出端連接該時鐘樹對應的第一相鄰時鐘樹中第二路徑選擇單元的第一輸入端,所述第一路徑選擇單元的第二輸出端連接該時鐘樹對應的第二相鄰時鐘樹中第二路徑選擇單元的第二輸入端;

14、所述第二路徑選擇單元的第一輸入端連接所述第二相鄰時鐘樹中第一路徑選擇單元的第一輸出端,所述第二路徑選擇單元的第二輸入端連接所述第一相鄰時鐘樹中第一路徑選擇單元的第二輸出端,所述第二路徑選擇單元的第一輸出端連接所述第二相鄰時鐘樹中第二路徑選擇單元的第三輸入端,所述第二所述第二路徑選擇單元的第三輸出端連接所述第一相鄰路徑選擇單元的第二輸出端連接所述第三路徑選擇單元的第一輸入端,時鐘樹中第三路徑選擇單元的第二輸入端;

15、第三路徑選擇單元的第二輸入端連接所述第二相鄰時鐘樹中第二路徑選擇單元的第三輸出端,第三路徑選擇單元的輸出端作為所述時鐘樹的末端葉節點。

16、在本發明實施例提出的多bank時鐘偏移調節電路中,通過上述第一路徑選擇單元、第二路徑選擇單元和第三路徑選擇單元實現不同信號傳輸路徑的分支,從而能夠根據時鐘源和io端口的位置關系,靈活選擇不同的信號傳輸路徑,并能夠同步且穩定地將時鐘源信號傳輸到相應的io端口,從而在不占用fpga自身時鐘管理資源的前提下,提高四bank之間的時序一致性。

17、此外,通過數據選擇器和緩沖器構建路徑選擇單元,其中數據選擇器和緩沖器互相配置,實現不同信號傳輸路徑的選擇,同時利用緩沖器實現對時鐘源信號的驅動,提高了信號傳輸路徑的傳輸能力,從而在有效減少四bank之間時鐘偏移誤差的同時,保證時鐘源信號的穩定傳輸。

18、可選的,在本發明的一些實施例中,在四bank組合使用的情況下,在每個所述時鐘樹中,所述第一路徑選擇單元的第三輸出端連接所述第三路徑選擇單元的第三輸入端,所述第一路徑選擇單元的第四輸出端連接所述第三路徑選擇單元的第四輸入端。

19、本發明實施例提出的所述多bank時鐘偏移調節電路在適用于多bank組合使用的應用場景的同時,還考慮到單獨使用一bank的應用場景,提出了在一個時鐘樹中的第一路徑選擇單元和第三路徑選擇單元直接連接的電路結構,從而提高所述多bank時鐘偏移調節電路在不同bank數量上的兼容性。

20、可選的,在本發明的一些實施例中,在三bank組合使用的情況下,每個所述時鐘樹包括:

21、第四路徑選擇單元以及第五路徑選擇單元;

22、其中,所述第四路徑選擇單元的輸入端連接所述時鐘源信號,所述第四路徑選擇單元的第一輸出端連接所述第五路徑選擇單元的第一輸入端,所述第四路徑選擇單元的第二輸出端連接該時鐘樹對應的第一相鄰時鐘樹中第五路徑選擇單元的第二輸入端,所述第四路徑選擇單元的第三輸出端連接該時鐘樹對應的第二相鄰時鐘樹中第五路徑選擇單元的第三輸入端;

23、所述第五路徑選擇單元的第二輸入端連接所述第二相鄰時鐘樹中第四路徑選擇單元的第二輸出端,所述第五路徑選擇單元的第三輸入端連接所述第一相鄰時鐘樹中第四路徑選擇單元的第三輸出端,所述第五路徑選擇單元的第四輸入端連接所述第二相鄰時鐘樹中第五路徑選擇單元的第一輸出端,所述第五路徑選擇單元的第五輸入端連接所述第一相鄰時鐘樹中第五路徑選擇單元的第二輸出端;

24、所述第五路徑選擇單元的第一輸出端連接所述第一相鄰時鐘樹中第五路徑選擇單元的第四輸入端,所述第五路徑選擇單元的第二輸出端連接所述第二相鄰時鐘樹中第五路徑選擇單元的第五輸入端,所述第五路徑選擇單元的第三輸出端作為所述時鐘樹的末端葉節點。

25、在本發明實施例提出的多bank時鐘偏移調節電路中,通過上述第四路徑選擇單元和第五路徑選擇單元實現不同信號傳輸路徑的分支,從而能夠根據時鐘源和io端口的位置關系,靈活選擇不同的信號傳輸路徑,并能夠同步且穩定地將時鐘源信號傳輸到相應的io端口,從而在不占用fpga自身時鐘管理資源的前提下,提高三bank之間的時序一致性。

26、此外,通過數據選擇器和緩沖器構建路徑選擇單元,其中數據選擇器和緩沖器互相配置,實現不同信號傳輸路徑的選擇,同時利用緩沖器實現對時鐘源信號的驅動,提高了信號傳輸路徑的傳輸能力,從而在有效減少三bank之間時鐘偏移誤差的同時,保證時鐘源信號的穩定傳輸。

27、可選的,在本發明的一些實施例中,每個所述時鐘樹的末端葉節點設有時鐘對齊電路,以便將偏移調節后的時鐘信號與可編程邏輯單元輸出的時鐘信號對齊。

28、通過在時鐘樹的末端葉節點設置時鐘對齊電路,能夠將時鐘樹末端葉節點輸出的偏移調節后的時鐘源信號與fpga可編程邏輯單元中邏輯陣列時鐘進行對齊,有利于提高fpga整體的時序管理效果。

29、第二方面,本發明實施例提出了一種fpga芯片,所述fpga芯片的io端口被劃分為多bank,每一所述bank設置有上述實施例所述的多bank時鐘偏移調節電路。

30、本發明實施例對應每一bank分別設置一個時鐘樹,并將相鄰bank對應的時鐘偏移調節電路級聯,從而在多bank之間建立若干個長度相等的信號傳輸路徑。在需要多個bank組合使用的情況下,多個bank能夠使用同一時鐘源發出的時鐘信號,并經上述長度相等的信號傳輸路徑達到各個bank對應的io端口,使得同一時鐘源信號在不同bank對應的時鐘樹之間傳輸時具有一致的延遲特性,減少了由于信號傳輸路徑長度差異引起的時鐘偏差,實現多bank組合使用時的時鐘對齊收斂。

31、相比現有的時鐘對齊方法,本發明實施例提出的上述多bank時鐘偏移調節電路具有節省fpga時鐘管理資源、降低時鐘延遲的優點,能夠提高多bank之間的時鐘偏移調節效果,降低了多bank之間時鐘對齊電路的設計與調試難度。

32、綜上可知,本發明實施例提出的多bank時鐘偏移調節電路與現有技術相比,其有益效果在于:

33、在本發明實施例提出的多bank時鐘偏移調節電路中,所述時鐘樹是在各個bank的時鐘源側設置的,因此相比于依靠fpga自身時鐘結構的傳統時鐘偏移調節方式,本發明實施例無需將時鐘源信號先傳輸到fpga自身的時鐘結構,再傳輸到不同bank對應的io端口,而是直接將同一時鐘源信號經各個bank對應設置的所述信號傳輸路徑傳輸到對應io端口,不僅能夠縮短了時鐘源信號的傳輸距離,降低了時鐘源信號到達各個bank對應io端口的延遲時間,而且能夠節省fpga自身的時鐘管理資源,降低了時鐘管理難度。

34、另外,本發明實施例通過所述數據選擇器和所述緩沖器能夠靈活實現不同信號傳輸路徑的選擇,同時能夠利用所述緩沖器對時鐘源信號的驅動能力,提高信號傳輸路徑的傳輸性能,保證時鐘源到達各個bank對應io端口的信號強度,因此提高了多bank之間時鐘偏移調節的可靠性與靈活性。

35、由此可見,基于同一個時鐘源,經所述信號傳輸路徑達到各個bank對應的io端口時均能夠得到有效的時鐘偏移調節,從而保證了不同bank之間的時鐘信號的同步性,提高了fpga整體的時序性能。

- 還沒有人留言評論。精彩留言會獲得點贊!