一種P溝道SONOS存儲器陣列及其操作方法與流程

本發明涉及半導體集成電路制造領域,具體涉及一種p溝道sonos存儲器陣列及其操作方法。

背景技術:

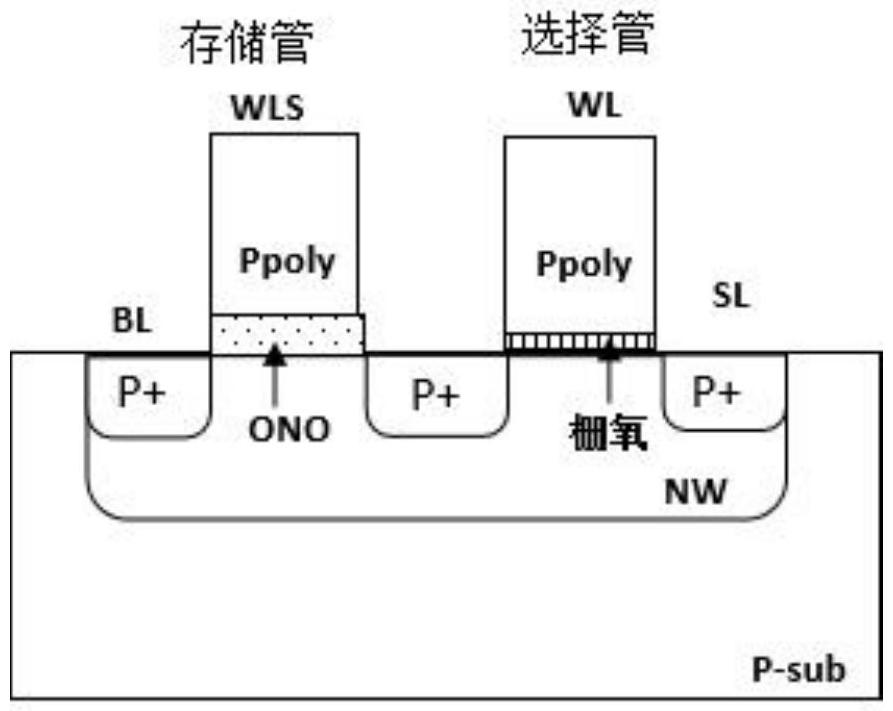

1、傳統的n溝道兩管sonos存儲器由一個n溝道sonos存儲管和一個n溝道選擇管在p阱(pw)中組成,如圖1所示,在sonos的e/p操作過程中,需要在p阱加正壓,為了隔離p阱和p型襯底,需要引入深n阱(dnw),在工藝制造過程中就需要使用深n阱的光罩來定義深n阱注入區域。

技術實現思路

1、有鑒于此,本發明提供一種p溝道sonos存儲器陣列及其操作方法,解決了在制造工藝中需使用深n阱的光罩的問題,節省工藝成本。

2、本發明提供一種p溝道sonos存儲器陣列,包括:

3、p型襯底;

4、n阱,位于所述p型襯底中;

5、第一和第二多晶硅柵,位于所述n阱上方;以及

6、源極和漏極,位于所述第一和第二多晶硅柵兩側的所述n阱中且均為p型摻雜;

7、所述第一多晶硅柵包括ono介質層和位于所述ono介質層上方的第一多晶硅柵極;所述第二多晶硅柵包括柵氧層和位于所述柵氧層上方的第二多晶硅柵極。

8、優選地,所述p型襯底為p型硅襯底。

9、優選地,所述第一和第二多晶硅柵極均為p型摻雜多晶硅柵極。

10、優選地,所述ono介質層為三層的疊層結構,包括隧穿氧化層、電荷存儲層和阻擋氧化層。

11、本發明還提供一種p溝道sonos存儲器陣列的操作方法,包括:

12、對所述p溝道sonos存儲器陣列進行擦除操作時,n阱接地,選中行的第一多晶硅柵極接第一正壓vpos,非選中行的第一多晶硅柵極接地,第二多晶硅柵極接地,源極和漏極均float;

13、對所述p溝道sonos存儲器陣列進行寫操作時,n阱接第一正壓vpos,第二多晶硅柵極接第一正壓vpos,選中行的第一多晶硅柵極接地,非選中行的第一多晶硅柵極接第二正壓vposu,漏極浮置,對寫“1”的單元,源極接vpos;對寫“0”的單元,源極接第三正壓vbl;

14、對所述p溝道sonos存儲器陣列進行讀取操作時,對選中單元的源極加第四正壓vlim,第二多晶硅柵極接地,其余端接第五正壓vpwr,讀取源端的電流即可獲得選中單元的狀態。

15、優選地,所述第一正壓vpos為7~12v,所述第二正壓vposu為6~10v,所述第三正壓vbl為3.5~6v,第四正壓vpwr為1.5~2.5v,所述第五正壓vlim為1~1.8v。

16、優選地,在寫入“0”后,存儲電荷狀態未改變,溝道表面聚集電子,sonos處于開啟狀態。

17、優選地,在寫入“1”后,存儲電荷狀態改變,sonos處于關斷狀態。

18、優選地,在擦除時,溝道表面聚集空穴,sonos處于開啟狀態。

19、本發明的p溝道sonos存儲器陣列,使用p型溝道和n阱,操作過程中n阱中加正壓不影響p型襯底電壓(pn結反偏),因此不需要引入深n阱來隔離,在制造工藝中可節省一張深n阱的光罩。本發明的p溝道sonos存儲器陣列操作方式可以省去n阱和p型襯底之間的隔離層。

技術特征:

1.一種p溝道sonos存儲器陣列,其特征在于,包括:

2.根據權利要求1所述的p溝道sonos存儲器陣列,其特征在于,所述p型襯底為p型硅襯底。

3.根據權利要求1所述的p溝道sonos存儲器陣列,其特征在于,所述第一和第二多晶硅柵極均為p型摻雜多晶硅柵極。

4.根據權利要求1所述的p溝道sonos存儲器陣列,其特征在于,所述ono介質層為三層的疊層結構,包括隧穿氧化層、電荷存儲層和阻擋氧化層。

5.一種如權利要求1-4所述的p溝道sonos存儲器陣列的操作方法,其特征在于,包括:

6.根據權利要求5所述的p溝道sonos存儲器陣列的操作方法,其特征在于,所述第一正壓vpos為7~12v,所述第二正壓vposu為6~10v,所述第三正壓vbl為3.5~6v,第四正壓vpwr為1.5~2.5v,所述第五正壓vlim為1~1.8v。

7.根據權利要求5所述的p溝道sonos存儲器陣列的操作方法,其特征在于,在寫入“0”后,存儲電荷狀態未改變,溝道表面聚集電子,sonos處于開啟狀態。

8.根據權利要求5所述的p溝道sonos存儲器陣列的操作方法,其特征在于,在寫入“1”后,存儲電荷狀態改變,sonos處于關斷狀態。

9.根據權利要求5所述的p溝道sonos存儲器陣列的操作方法,其特征在于,在擦除時,溝道表面聚集空穴,sonos處于開啟狀態。

技術總結

本發明提供一種P溝道SONOS存儲器陣列,包括P型襯底;位于P型襯底內的N阱;位于N阱上的第一和第二多晶硅柵,第一多晶硅柵包括ONO介質層和位于ONO介質層上方的第一多晶硅柵極;第二多晶硅柵包括柵氧層和位于柵氧層上方的第二多晶硅柵極;以及位于第一和第二多晶硅柵兩側的N阱中且均為P型摻雜的源極和漏極。本發明還提供一種P溝道SONOS存儲器陣列的操作方法,在N阱、第一和第二多晶硅柵極、源極和漏極施加各操作電壓,以實現對P溝道SONOS存儲器陣列的寫入、擦除和讀取操作。本發明的P溝道SONOS存儲器陣列使用P型溝道和N阱,操作過程中N阱中加正壓不影響P型襯底電壓,因此不需要引入深N阱來隔離,在制造工藝中可節省一張深N阱的光罩。

技術研發人員:王寧,張可鋼

受保護的技術使用者:上海華虹宏力半導體制造有限公司

技術研發日:

技術公布日:2024/10/21

- 還沒有人留言評論。精彩留言會獲得點贊!