半導體裝置的制作方法

本發明構思涉及一種半導體裝置。

背景技術:

1、半導體裝置可提供驅動器和用于與外部半導體裝置交換信號的接收器。驅動器可連接到輸出信號的焊盤,并且可包括根據操作模式調整輸出信號的擺動范圍和擺動電平的功能。然而,隨著輸出信號的擺動范圍和擺動電平的改變,輸出信號的占空比可能被無意地改變,并且在這種情況下,可能出現諸如輸出信號的信號完整性(si)特性劣化的問題。因此,希望即使在輸出信號的擺動范圍和擺動電平改變時也使輸出信號的si特性的劣化最小化。

技術實現思路

1、本發明構思的一方面在于提供一種半導體裝置,即使當輸出信號的擺動電平和擺動范圍根據操作模式改變時,該半導體裝置也能夠通過穩定地保持輸出信號的占空比來使si特性的劣化最小化。

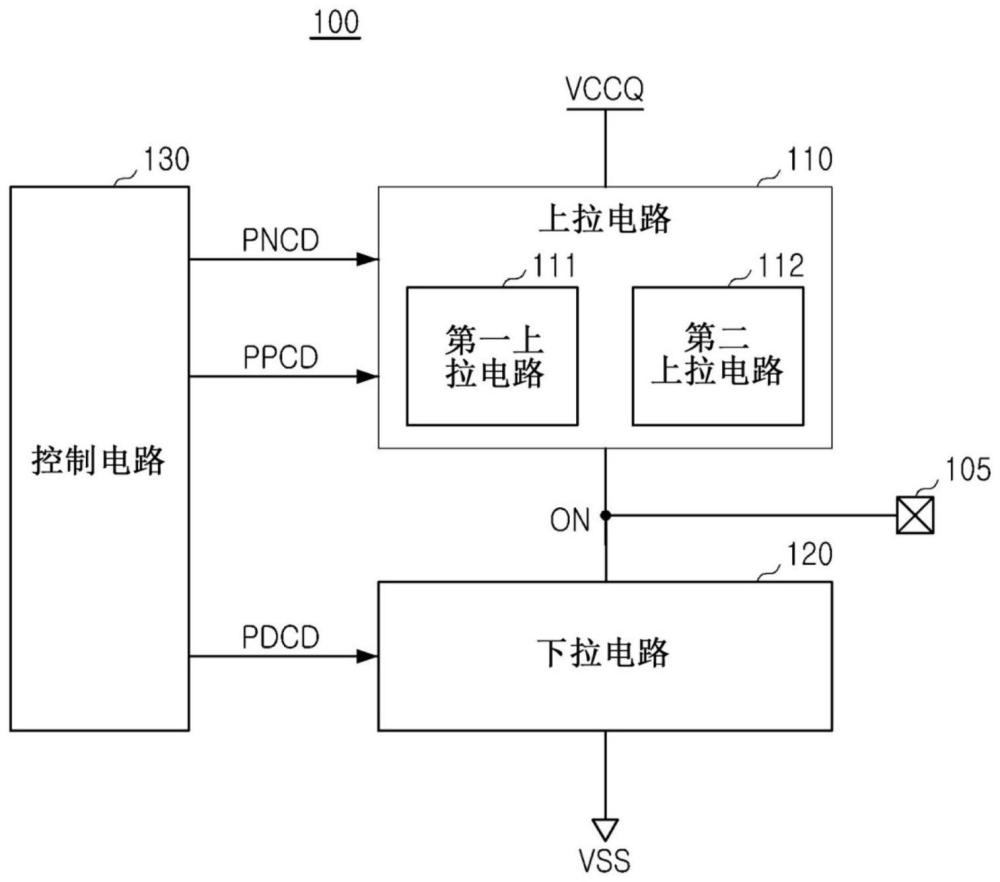

2、根據本發明構思的一方面,一種半導體裝置包括:上拉電路,其連接在供應第一電源電壓的第一電源節點和信號通過其被輸出的輸出節點之間;下拉電路,其連接在供應低于第一電源電壓的第二電源節點和輸出節點之間;以及控制電路,其控制上拉電路和下拉電路。上拉電路包括第一上拉電路和第二上拉電路,第一上拉電路包括連接在第一電源節點和輸出節點之間的多個nmos晶體管,第二上拉電路包括連接在第一電源節點和輸出節點之間的多個pmos晶體管。在半導體裝置的第一操作模式中,信號在與第二電源電壓對應的第一低電平與低于第一電源電壓的第一高電平之間擺動,控制電路向第一上拉電路輸出第一上拉代碼,并向第二上拉電路輸出第二上拉代碼。第二上拉電路的多個pmos晶體管中的至少一個基于第二上拉代碼被導通。

3、根據本發明構思的一方面,一種半導體裝置包括:第一驅動器電路,其被配置為向第一焊盤輸出第一信號;第二驅動器電路,其被配置為向不同于第一焊盤的第二焊盤輸出與第一信號互補的第二信號;以及控制電路,其被配置為控制第一驅動器電路和第二驅動器電路。控制電路包括:緩沖器,其包括連接到第一焊盤和第二焊盤的輸入端子以及輸出基于第一信號和第二信號之間的差的數字信號的輸出端子;積分器,其被配置為響應于數字信號進行操作;比較器,其被配置為將積分器的輸出電壓與參考電壓進行比較;以及計數器,其被配置為基于比較器的比較結果輸出n位代碼(其中,n是等于或大于2的自然數)。基于n位代碼來調整第一驅動器電路的上拉電路的電阻和第二驅動器電路的上拉電路的電阻。

4、根據本發明構思的一方面,一種半導體裝置包括:上拉電路,其包括連接在供應第一電源電壓的第一電源節點和信號通過其被輸出的輸出節點之間并包括多個nmos晶體管的第一上拉電路;第二上拉電路,其在所述第一電源節點與輸出節點之間并聯連接到第一上拉電路,并且包括多個pmos晶體管;以及控制電路,其被配置為向第一上拉電路輸出第一上拉代碼,并向第二上拉電路輸出第二上拉代碼。在半導體裝置的第一操作模式中,信號在對應于低于第一電源電壓的第二電源電壓的第一低電平與低于第一電源電壓1/2倍的第一高電平之間擺動,基于第一上拉代碼確定第一上拉電路的電阻,并且基于第二上拉代碼確定第二上拉電路的電阻。上拉電路的總電阻小于第一上拉電路的電阻和第二上拉電路的電阻。

技術特征:

1.一種半導體裝置,包括:

2.如權利要求1所述的半導體裝置,其中,在所述第一操作模式中,所述半導體裝置被配置為使得所述控制電路:

3.如權利要求2所述的半導體裝置,其中,所述控制電路被配置為:

4.如權利要求1所述的半導體裝置,其中,所述控制電路將所述第一上拉代碼輸入到所述第一上拉電路的時段比所述控制電路將所述第二上拉代碼輸入到所述第二上拉電路的時段長。

5.如權利要求4所述的半導體裝置,其中,所述控制電路向所述第二上拉電路輸出所述第二上拉代碼的時段與所述信號的上升時段重疊。

6.如權利要求1所述的半導體裝置,其中,所述第一上拉代碼的位的數量等于所述第二上拉代碼的位的數量。

7.如權利要求1所述的半導體裝置,其中,在所述半導體裝置的第二操作模式中:

8.如權利要求7所述的半導體裝置,其中,所述第二低電平等于所述第一高電平。

9.如權利要求1所述的半導體裝置,其中,所述第一高電平是所述第一電源電壓的1/3倍。

10.如權利要求1所述的半導體裝置,其中,所述控制電路包括:

11.如權利要求10所述的半導體裝置,其中,所述緩沖器的所述輸出信號是在地電壓與電源電壓之間擺動的數字信號,并且

12.一種半導體裝置,包括:

13.如權利要求12所述的半導體裝置,其中,所述積分器包括被配置為基于所述數字信號被充電或放電的多個泵浦電容器。

14.如權利要求12所述的半導體裝置,其中,當所述積分器的所述輸出電壓高于所述參考電壓時,所述半導體裝置被配置為使得所述計數器輸出所述n位代碼以增大所述第一驅動器電路和所述第二驅動器電路中的每一個的上拉電路的電阻。

15.如權利要求12所述的半導體裝置,其中,當所述積分器的所述輸出電壓低于所述參考電壓時,所述半導體裝置被配置為使得所述計數器輸出所述n位代碼以減小所述第一驅動器電路和所述第二驅動器電路中的每一個的所述上拉電路的電阻。

16.如權利要求12所述的半導體裝置,其中,所述緩沖器是全差分放大器。

17.如權利要求12所述的半導體裝置,其中,所述第一驅動器電路和所述第二驅動器電路中的每一個的上拉電路包括第一上拉電路和第二上拉電路,所述第一上拉電路包括多個nmos晶體管,所述第二上拉電路包括多個pmos晶體管,

18.如權利要求17所述的半導體裝置,其中,所述控制電路被配置為向所述第一驅動器電路和所述第二驅動器電路中的每一個的所述第一上拉電路輸出在所述半導體裝置的zq校準操作中確定的代碼。

19.一種半導體裝置,包括:

20.如權利要求19所述的半導體裝置,還包括:

技術總結

一種半導體裝置包括:第一上拉電路,其連接在供應第一電源電壓的第一電源節點和信號通過其被輸出的輸出節點之間,并包括多個NMOS晶體管;第二上拉電路,其在第一電源節點與輸出節點之間并聯連接到第一上拉電路,并且包括多個PMOS晶體管;以及控制電路,其將第一上拉代碼輸出到第一上拉電路,并將第二上拉代碼輸出到第二上拉電路。在第一操作模式中,信號在低于第一電源電壓的第一低電平與低于第一電源電壓的1/2倍的第一高電平之間擺動,基于第一上拉代碼確定第一上拉電路的電阻,并且基于第二上拉代碼確定第二上拉電路的電阻。

技術研發人員:姜玄錫,李政秀,安恩志,樸廷埈,尹治元

受保護的技術使用者:三星電子株式會社

技術研發日:

技術公布日:2024/10/21

- 還沒有人留言評論。精彩留言會獲得點贊!