半導體元件結構的制作方法

本公開涉及一種半導體元件結構及其制備方法。尤其涉及一種包括一中介層的半導體元件結構。

背景技術:

1、隨著電子產業的快速發展,集成電路(ics)的發展已經達到高效能以及小型化。在ic材料以及設計的技術進步產生了數代的ics,而其每一代均具有比上一代更小、更復雜的電路。

2、例如一快閃存儲器、一動態隨機存取存儲器(dram)即類似物的存儲器被用來儲存來自邏輯電路的數據。最近,包括存儲器與邏輯電路的一半導體元件結構在微型化方面面臨著巨大的挑戰。因此,需要一種新的半導體元件結構。

3、上文的“現有技術”說明僅提供背景技術,并未承認上文的“現有技術”說明公開本公開的標的,不構成本公開的現有技術,且上文的“現有技術”的任何說明均不應作為本案的任一部分。

技術實現思路

1、本公開的目的在于提出一種半導體元件結構,以解決上述至少一個問題。

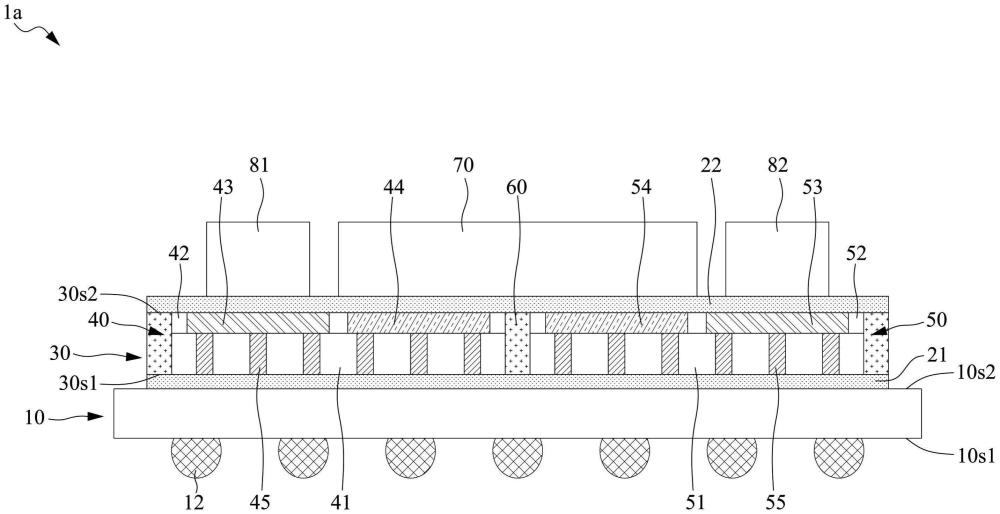

2、本公開的一實施例提供一種半導體元件結構。該半導體元件結構包括一中介層、一第一重分布結構以及一第一電子元件。該中介層具有一第一表面以及與該第一表面相對的一第二表面,該中介層包括一第一半導體裸片,該第一半導體裸片包括一第一快閃存儲器以及一第一存儲器控制電路。第一重分布結構設置在該第二表面上。第一電子元件設置在該第一重分布結構上,其中該第一電子元件電性連接至該第一快閃存儲器。

3、本公開的多個所述實施例提供一半導體元件結構。該半導體元件結構包括一中介層,該中介層包括一快閃存儲器,形成在一半導體裸片內。邏輯電路設置在另一個電子元件中,其減小了所述電子元件的尺寸。在一比較例中,邏輯電路與快閃存儲器整合在一個裸片中,其增加了裸片的尺寸并且不利地影響了半導體元件結構的小型化。在一些實施例中,該中介層包括兩個或更多個半導體裸片。每個半導體裸片包括一快閃存儲器以及一存儲器控制電路。邏輯電路可以與任何一個半導體裸片進行通信連接,或者與兩個或更多半導體裸片進行通信連接。這樣的設計可以改善制造一半導體元件結構的良率。

4、上文已相當廣泛地概述本公開的技術特征及優點,以使下文的本公開詳細描述得以獲得較佳了解。構成本公開的權利要求標的的其它技術特征及優點將描述于下文。本公開所屬技術領域中技術人員應了解,可相當容易地利用下文公開的概念與特定實施例可作為修改或設計其它結構或工藝而實現與本公開相同的目的。本公開所屬技術領域中技術人員亦應了解,這類等效建構無法脫離隨附的權利要求所界定的本公開的精神和范圍。

技術特征:

1.一種半導體元件結構,包括:

2.如權利要求1所述的半導體元件結構,其中該中介層還包含一第二半導體裸片,且該第二半導體裸片包括一第二快閃存儲器以及一第二存儲器控制電路。

3.如權利要求2所述的半導體元件結構,其中該第一電子元件通過該第一重分布結構與該第一半導體裸片及/或該第二半導體裸片進行通信連接。

4.如權利要求2所述的半導體元件結構,其中該第一電子元件重疊該第一半導體裸片以及該第二半導體裸片。

5.如權利要求2所述的半導體元件結構,其中該第一快閃存儲器比該第一存儲器控制電路更靠近該第二快閃存儲器。

6.如權利要求2所述的半導體元件結構,其中該第一快閃存儲器比該第二快閃存儲器更靠近該第二存儲器控制電路。

7.如權利要求2所述的半導體元件結構,其中該中介層包含:

8.如權利要求7所述的半導體元件結構,其中該第一重分布結構覆蓋該第一半導體裸片、該第二半導體裸片以及該封裝膠體。

9.如權利要求1所述的半導體元件結構,還包含:

10.如權利要求9所述的半導體元件結構,其中該第二電子元件包括一動態隨機存取存儲器。

11.如權利要求9所述的半導體元件結構,其中該第二電子元件重疊該第一存儲器控制電路。

12.如權利要求1所述的半導體元件結構,還包含:

13.如權利要求12所述的半導體元件結構,其中該第一半導體裸片包括一貫穿通孔,在該第一快閃存儲器與該第二重分布結構之間延伸。

14.如權利要求12所述的半導體元件結構,其中該中介層包含一封裝膠體,封裝該第一半導體裸片,該封裝膠體設置在該第一重分布結構與該第二重分布結構之間。

技術總結

本公開提供一種半導體元件結構。該半導體元件結構包括一中介層、一第一重分布結構以及一第一電子元件。該中介層具有一第一表面以及與該第一表面相對的一第二表面,該中介層包括一第一半導體裸片,該第一半導體裸片包括一第一快閃存儲器以及一第一存儲器控制電路。第一重分布結構設置在該第二表面上。第一電子元件設置在該第一重分布結構上,其中該第一電子元件電性連接至該第一快閃存儲器。

技術研發人員:施信益

受保護的技術使用者:南亞科技股份有限公司

技術研發日:

技術公布日:2024/10/21

- 還沒有人留言評論。精彩留言會獲得點贊!