半導體裝置的制作方法

本公開涉及一種半導體裝置,并且更具體地,涉及一種包括多柵極結構的半導體裝置。

背景技術:

1、半導體裝置由于其小尺寸、多功能性和/或低制造成本而在電子工業中具有重要作用。半導體裝置可以被分類為存儲邏輯數據的半導體存儲器裝置、處理邏輯數據的操作的半導體邏輯裝置、以及具有存儲器和邏輯元件兩者的混合半導體裝置中的一種。

2、近來,電子產品的高速和低消耗要求嵌入在電子產品中的半導體裝置應當具有高操作速度和/或較低的工作電壓,因此,為了滿足這些要求的特性,半導體裝置被高度集成,并且為此目的已經進行了各種研究。

技術實現思路

1、本公開的目的是提供一種具有改進的集成度的半導體裝置。

2、本公開的目的是提供一種具有改善的電特性的半導體裝置。

3、由本發明的實施例解決的問題不限于上述問題,并且本領域技術人員通過下面的描述將清楚地理解其它未提及的益處。

4、根據本公開的一些實施例的半導體裝置可以包括:外部有源圖案,其在襯底上,外部有源圖案具有與外部有源圖案交叉的溝槽;外部字線,其覆蓋溝槽的壁;內部有源圖案,其在溝槽中覆蓋外部字線;內部字線,其在溝槽中覆蓋內部有源圖案;以及分離絕緣圖案,其在溝槽中插置在外部字線與內部有源圖案之間。外部字線和內部字線可以彼此絕緣。外部字線可以包括外部柵電極和外部電介質圖案,外部柵電極位于外部有源圖案和分離絕緣圖案之間,外部電介質圖案位于外部柵電極和外部有源圖案之間。內部字線可以包括內部柵電極和內部電介質圖案,內部柵電極在溝槽中覆蓋內部有源圖案,內部電介質圖案位于內部柵電極和內部有源圖案之間。外部有源圖案與外部柵電極可以通過外部電介質圖案位于其間而間隔開。內部有源圖案與內部柵電極可以通過內部電介質圖案插置在其間而間隔開。

5、根據本公開的一些實施例的半導體裝置可以包括:外部有源圖案,其在襯底上,外部有源圖案具有與外部有源圖案交叉的溝槽;外部字線,其覆蓋溝槽的壁;內部有源圖案,其在溝槽中覆蓋外部字線;內部字線,其在溝槽中覆蓋內部有源圖案;分離絕緣圖案,其在溝槽中插置在外部字線與內部有源圖案之間;外部位線和外部數據存儲圖案,外部位線和外部數據存儲圖案分別電連接至外部有源圖案;以及內部位線和內部數據存儲圖案,內部位線和內部數據存儲圖案分別電連接至內部有源圖案。外部有源圖案可以包括其上部的一對外部源極/漏極區。內部有源圖案可以包括其上部的一對內部源極/漏極區。外部位線可以電連接至一對外部源極/漏極區中的一個。內部位線可以電連接至一對內部源極/漏極區中的一個。

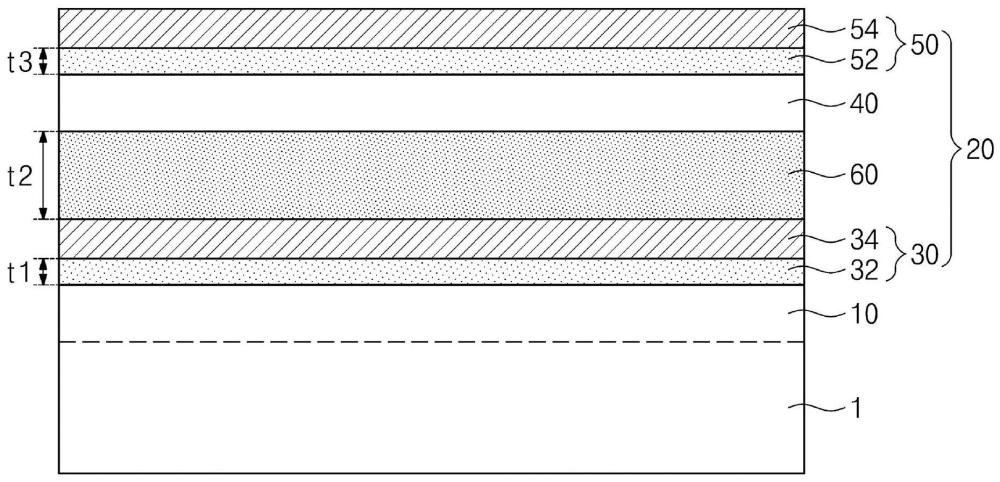

6、根據本公開的一些實施例的半導體裝置可以包括:第一有源圖案,其在襯底上;第二有源圖案,其在第一有源圖案上;分離絕緣圖案,其位于第一有源圖案和第二有源圖案之間;第一字線,其位于第一有源圖案和分離絕緣圖案之間;以及第二字線,其在第二有源圖案上。第一字線與第二字線彼此絕緣。第一字線包括第一柵電極和第一電介質圖案,第一柵電極位于第一有源圖案和分離絕緣圖案之間,第一電介質圖案位于第一有源圖案和第一柵電極之間。第二字線包括第二柵電極和第二電介質圖案,第二柵電極在第二有源圖案上,第二電介質圖案位于第二有源圖案和第二柵電極之間。分離絕緣圖案的厚度分別大于或基本上等于第一電介質圖案的厚度和第二電介質圖案的厚度。

技術特征:

1.一種半導體裝置,包括:

2.根據權利要求1所述的半導體裝置,其中,所述分離絕緣圖案將所述外部字線與所述內部有源圖案分離。

3.根據權利要求1所述的半導體裝置,其中,所述分離絕緣圖案的厚度分別大于或等于所述外部電介質圖案的厚度和所述內部電介質圖案的厚度兩者。

4.根據權利要求1所述的半導體裝置,其中,所述分離絕緣圖案包括絕緣材料。

5.根據權利要求1所述的半導體裝置,其中,所述外部有源圖案包括所述外部有源圖案的上部上的一對外部源極/漏極區,并且

6.根據權利要求5所述的半導體裝置,其中,所述外部有源圖案還包括沿著所述壁在所述一對外部源極/漏極區之間延伸的外部溝道區,并且

7.根據權利要求5所述的半導體裝置,其中,所述一對內部源極/漏極區插置在所述一對外部源極/漏極區之間。

8.根據權利要求1所述的半導體裝置,其中,所述內部有源圖案包括半導體材料。

9.根據權利要求1所述的半導體裝置,其中,所述外部有源圖案圍繞所述溝槽中的所述外部字線,并且

10.根據權利要求1所述的半導體裝置,其中,所述外部有源圖案在平行于所述襯底的下表面的第一方向上延伸,

11.根據權利要求1所述的半導體裝置,還包括多個外部有源圖案,并且

12.根據權利要求11所述的半導體裝置,其中,所述內部字線與所述多個外部有源圖案中的每個外部有源圖案交叉。

13.一種半導體裝置,包括:

14.根據權利要求13所述的半導體裝置,其中,所述外部數據存儲圖案電連接到所述一對外部源極/漏極區中的另一個外部源極/漏極區,并且

15.根據權利要求13所述的半導體裝置,其中,所述內部位線和所述內部數據存儲圖案插置在所述外部有源圖案和所述外部數據存儲圖案之間。

16.根據權利要求15所述的半導體裝置,其中,所述內部位線插置在所述外部位線與所述內部數據存儲圖案之間。

17.根據權利要求15所述的半導體裝置,其中,所述內部數據存儲圖案插置在所述外部位線與所述內部位線之間。

18.根據權利要求13所述的半導體裝置,其中,所述外部數據存儲圖案和所述內部數據存儲圖案中的每一個是包括下電極、電介質層和上電極的電容器。

19.一種半導體裝置,包括:

20.根據權利要求19所述的半導體裝置,其中,所述分離絕緣圖案將所述第一字線與所述第二有源圖案分離。

技術總結

一種半導體裝置,包括:外部有源圖案,其在襯底上,外部有源圖案具有與外部有源圖案交叉的溝槽;外部字線,其覆蓋溝槽的壁;內部有源圖案,其在溝槽中覆蓋外部字線;內部字線,其在溝槽中覆蓋內部有源圖案;以及分離絕緣圖案,其在溝槽中插置在外部字線和內部有源圖案之間。外部字線和內部字線彼此絕緣。

技術研發人員:李善行,孫東熙

受保護的技術使用者:三星電子株式會社

技術研發日:

技術公布日:2024/10/21

- 還沒有人留言評論。精彩留言會獲得點贊!