一種晶體管及制備方法

本發明涉及半導體,尤其涉及一種晶體管及制備方法。

背景技術:

1、基于有機半導體材料制備出的薄膜晶體管(thin-film?transistor,tft),與傳統的單晶硅金屬-氧化物-半導體場效應晶體管(mos-fet)相比,具備制備溫度低、可大面積制作、可在異質襯底上形成等優勢,因此被廣泛應用于顯示電子、柔性電子、透明電子、生物電子等領域。

2、有機半導體,自被發現以來,就因其具有本征柔性、工藝溫度低、可大面積集成等特點被廣泛關注,并作為一類薄膜晶體管有源區材料應用于生產中。隨著社會發展對薄膜晶體管電路速度的需求越來越高,電路功耗的標準要求越來越低,為了拓寬有機薄膜晶體管的應用范圍,有機薄膜晶體管的遷移率需要相應提高,溝道長度需要相應減小,關斷漏電流、柵泄漏電流及亞閾值擺幅需要相應減小。目前,有機薄膜晶體管種類繁多,但是在短溝道尺度下,受短溝道效應影響下具有高遷移率和穩定的低閾值電壓特性的有機薄膜晶體管只有少部分。而且大部分的有機薄膜晶體管受寄生溝道和電流旁路的影響很大,這增大了有機薄膜晶體管的關斷漏電流、柵泄漏電流及亞閾值擺幅,限制了有機薄膜晶體管電路的開關速度,極大的增加了有機薄膜晶體管電路的功耗。

技術實現思路

1、鑒于上述問題,提出了本發明以便提供一種克服上述問題或者至少部分地解決上述問題的晶體管及制備方法。

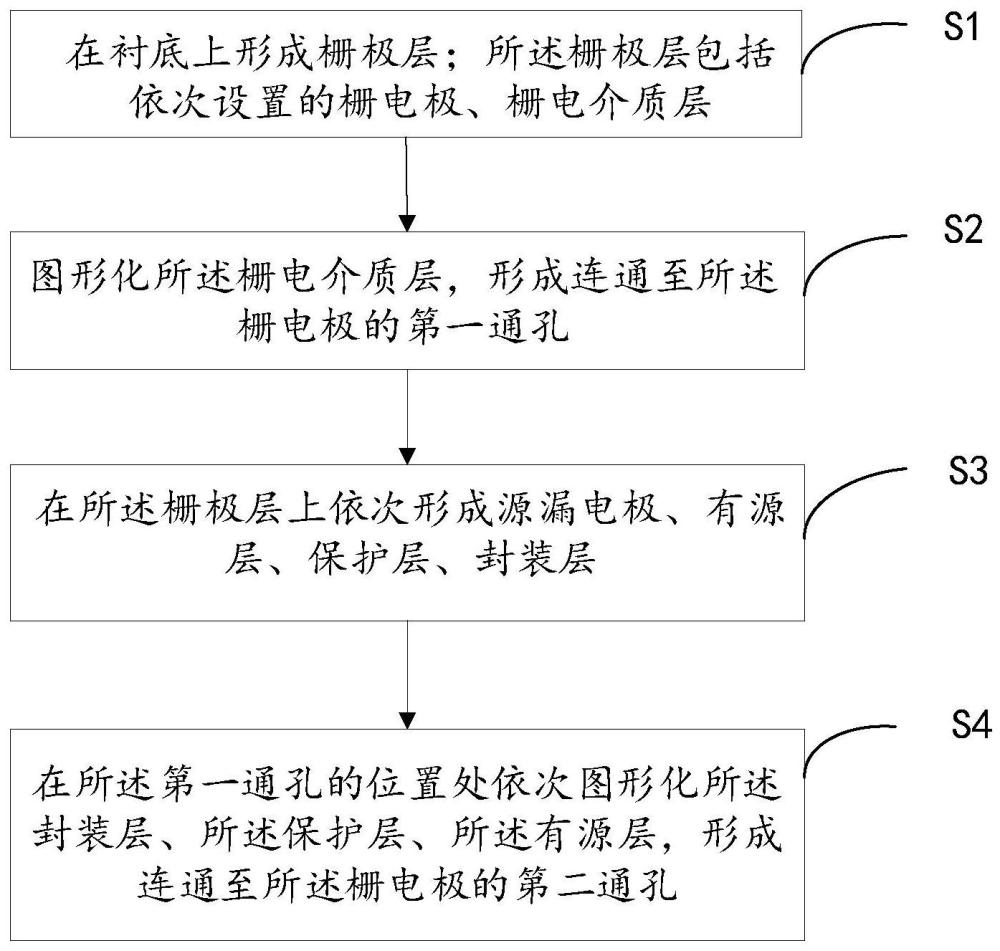

2、第一方面,提供一種晶體管制備方法,包括:在襯底上形成柵極層;所述柵極層包括依次設置的柵電極、柵電介質層;

3、圖形化所述柵電介質層,形成連通至所述柵電極的第一通孔;

4、在所述柵極層上依次形成源漏電極、有源層、保護層、封裝層;

5、在所述第一通孔的位置處依次圖形化所述封裝層、所述保護層、所述有源層,形成連通至所述柵電極的第二通孔。

6、可選的,所述在襯底上形成柵極層,包括:

7、在襯底上形成柵電極,圖形化所述柵電極,以露出所述襯底的部分表面;

8、在所述襯底表面、所述柵電極表面形成柵電介質層。

9、可選的,所述圖形化所述柵電介質層,形成連通至所述柵電極的第一通孔,包括:

10、通過干法刻蝕工藝對所述柵電介質層進行圖形化,形成第一通孔,所述柵電極的部分表面通過所述第一通孔露出。

11、可選的,所述在所述柵極層上依次形成源漏電極、有源層、保護層、封裝層,包括:

12、在所述柵電介質層上形成源漏電極;

13、圖形化所述源漏電極,以露出所述柵電介質層的部分表面;

14、對所述柵電介質層、所述源漏電極進行修飾;

15、在所述柵電介質層表面、源漏電極表面以及所述柵電極表面形成有源層;

16、在所述有源層上形成保護層;

17、在所述保護層上形成封裝層。

18、可選的,所述圖形化所述源漏電極,包括:

19、采用光刻和剝離工藝對所述源漏電極進行圖形化,使所述源漏電極之間的溝道長度為50nm~500μm。

20、可選的,所述對所述柵電介質層、所述源漏電極進行修飾,包括:

21、采用浸泡柵電介質修飾層溶液對所述柵電介質層進行修飾;

22、采用浸泡金屬修飾層溶液或熱蒸發修飾層對所述源漏電極進行修飾。

23、可選的,所述在所述第一通孔的位置處依次圖形化所述封裝層、所述保護層、所述有源層,形成連通至所述柵電極的第二通孔,包括:

24、采用光刻和氧等離子刻蝕工藝對所述第一通孔位置處的所述封裝層、所述保護層以及所述有源層進行圖形化,形成第二通孔,所述柵電極的部分表面通過所述第二通孔露出。

25、第二方面,提供一種晶體管,包括:襯底,以及依次設置在所述襯底上的柵極層、源漏電極、有源層、保護層、封裝層;

26、所述柵極層包括依次設置的柵電極、柵電介質層;

27、所述晶體管上設置通孔,所述通孔依次穿過所述封裝層、所述保護層、所述有源層以及所述柵電介質層并與所述柵電極連通。

28、可選的,所述柵電極的底面接觸并至少部分覆蓋所述襯底;所述源漏電極的底面接觸并至少部分覆蓋所述柵電介質層;所述有源層的底面接觸并覆蓋于所述柵電介質層表面、所述源漏電極表面。

29、可選的,所述有源層的厚度為2~4nm

30、本發明實施例中提供的技術方案,至少具有如下技術效果或優點:

31、本發明實施例提供的晶體管及制備方法,一方面,在柵電介質層形成通孔使柵電極露出,之后在有源層上形成保護層與封裝層,使有源層得以進行圖形化,同時避免圖形化操作損壞晶體管。另一方面,通過兩次圖案化操作,在同一位置處的柵電介質層與有源層上加工出通孔連接通至柵電極,實現了在有源層上進行圖案化,切斷了柵極與有源層之間的電流通路以及源漏電極之間未受柵極調控的有源層電流旁路,減小有機薄膜晶體管的關斷漏電流、柵泄漏電流及亞閾值擺幅,提升有機薄膜晶體管電路的開關速度,減少有機薄膜晶體管電路的功耗。

32、上述說明僅是本發明技術方案的概述,為了能夠更清楚了解本發明的技術手段,而可依照說明書的內容予以實施,并且為了讓本發明的上述和其它目的、特征和優點能夠更明顯易懂,以下特舉本發明的具體實施方式。

技術特征:

1.一種晶體管制備方法,其特征在于,包括:

2.如權利要求1所述的制備方法,其特征在于,所述在襯底上形成柵極層,包括:

3.如權利要求1所述的制備方法,其特征在于,所述圖形化所述柵電介質層,形成連通至所述柵電極的第一通孔,包括:

4.如權利要求1所述的制備方法,其特征在于,所述在所述柵極層上依次形成源漏電極、有源層、保護層、封裝層,包括:

5.如權利要求4所述的制備方法,其特征在于,所述圖形化所述源漏電極,包括:

6.如權利要求4所述的制備方法,其特征在于,所述對所述柵電介質層、所述源漏電極進行修飾,包括:

7.如權利要求1所述的制備方法,其特征在于,所述在所述第一通孔的位置處依次圖形化所述封裝層、所述保護層、所述有源層,形成連通至所述柵電極的第二通孔,包括:

8.一種晶體管,其特征在于,包括:

9.如權利要求8所述的晶體管,其特征在于,所述柵電極的底面接觸并至少部分覆蓋所述襯底;所述源漏電極的底面接觸并至少部分覆蓋所述柵電介質層;所述有源層的底面接觸并覆蓋于所述柵電介質層表面、所述源漏電極表面。

10.如權利要求8所述的晶體管,其特征在于,所述有源層的厚度為2~4nm。

技術總結

本發明公開了一種晶體管及制備方法,在襯底上形成柵極層;所述柵極層包括依次設置的柵電極、柵電介質層;圖形化所述柵電介質層,形成連通至所述柵電極的第一通孔;在所述柵極層上依次形成源漏電極、有源層、保護層、封裝層;在所述第一通孔的位置處依次圖形化所述封裝層、所述保護層、所述有源層,形成連通至所述柵電極的第二通孔。本發明通過兩次圖案化操作,在同一位置處的柵電介質層與有源層上加工出通孔連接通至柵電極,實現了在有源層上進行圖案化,減小有機薄膜晶體管的關斷漏電流、柵泄漏電流及亞閾值擺幅,提升有機薄膜晶體管電路的開關速度,減少有機薄膜晶體管電路的功耗。

技術研發人員:李蒙蒙,丁晨明,陸叢研,李泠,劉明

受保護的技術使用者:中國科學院微電子研究所

技術研發日:

技術公布日:2024/10/21

- 還沒有人留言評論。精彩留言會獲得點贊!