包括源極或發射極焊盤的垂直功率半導體裝置的制作方法

本公開涉及一種垂直功率半導體裝置,特別地涉及一種包括包含源極或發射極焊盤的配線層級的垂直功率半導體裝置。

背景技術:

1、新生代垂直功率半導體裝置(例如,金屬氧化物半導體場效應晶體管(mosfet)或絕緣柵雙極晶體管(igbt)或結型場效應晶體管(jfet))的技術開發旨在通過縮小裝置幾何形狀來改進電氣裝置特性并且減小成本。雖然通過縮小裝置幾何形狀可減小成本,但必須滿足各種折衷和挑戰。例如,當增加每單位面積的裝置功能時,符合可靠性要求需要例如針對互連件的設計優化。

2、因此,存在對改進的垂直功率半導體裝置的需要。

技術實現思路

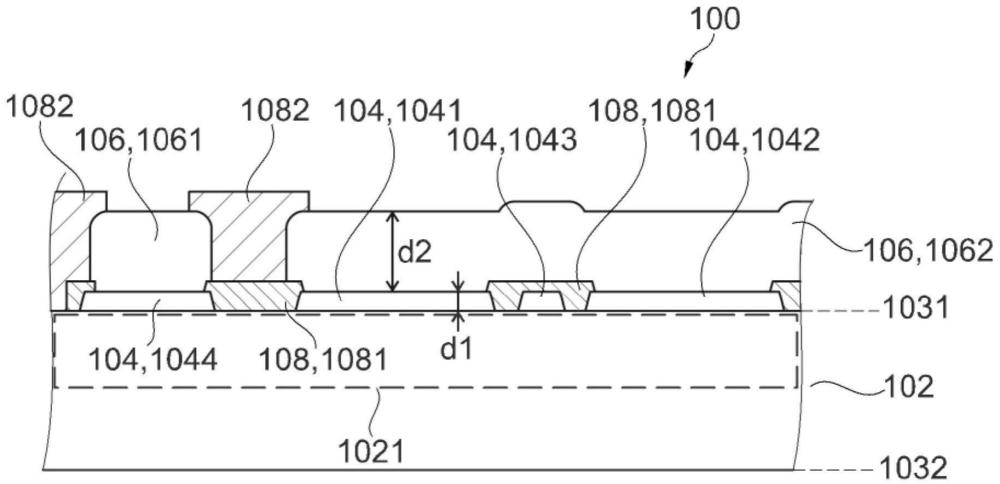

1、本公開的示例涉及一種垂直功率半導體裝置。垂直功率半導體裝置包括sic半導體主體,所述sic半導體主體具有第一表面和與第一表面相對的第二表面。垂直功率半導體裝置還在第一表面之上包括第一配線層級。第一配線層級包括第一下源極或發射極焊盤和第二下源極或發射極焊盤。垂直功率半導體裝置還在第一配線層級之上包括第二配線層級。第二配線層級包括柵極焊盤和源極或發射極焊盤。第二配線層級的源極或發射極焊盤按照電氣方式連接到第一配線層級的第一下源極或發射極焊盤和第二下源極或發射極焊盤。第一配線層級還包括沿側向布置在第一下源極或發射極焊盤和第二下源極或發射極焊盤之間的柵極線。柵極線沿垂直方向布置在第二配線層級的源極或發射極焊盤和第一表面之間。柵極線通過中間介電結構與第二配線層級的源極或發射極焊盤電絕緣。

2、本公開的另一示例涉及一種垂直功率半導體裝置。垂直功率半導體裝置包括sic半導體主體,所述sic半導體主體具有第一表面和與第一表面相對的第二表面。垂直功率半導體裝置還包括從第一表面延伸到sic半導體主體中的第一溝槽結構。垂直功率半導體裝置還包括從第一溝槽結構分叉的多個第二溝槽結構。第一溝槽結構的橫截面面積大于所述多個第二溝槽結構中的每個第二溝槽結構的橫截面面積。垂直功率半導體裝置還在第一表面之上包括配線層級。配線層級包括柵極焊盤和源極或發射極焊盤。

3、本公開的另一示例涉及一種制造垂直功率半導體裝置的方法。所述方法包括:在sic半導體主體的第一表面之上形成第一配線層級,所述sic半導體主體具有第一表面和與第一表面相對的第二表面。第一配線層級包括第一下源極或發射極焊盤和第二下源極或發射極焊盤。所述方法還包括:在第一配線層級之上形成第二配線層級。第二配線層級包括柵極焊盤和源極或發射極焊盤。第二配線層級的源極或發射極焊盤按照電氣方式連接到第一配線層級的第一下源極或發射極焊盤和第二下源極或發射極焊盤。第一配線層級還包括沿側向布置在第一下源極或發射極焊盤和第二下源極或發射極焊盤之間的柵極線。柵極線沿垂直方向布置在第二配線層級的源極或發射極焊盤和第一表面之間。柵極線通過中間介電結構與第二配線層級的源極或發射極焊盤電絕緣。

4、本公開的另一示例涉及一種制造垂直功率半導體裝置的方法。所述方法包括:形成從第一表面延伸到sic半導體主體中的第一溝槽結構,所述sic半導體主體具有第一表面和與第一表面相對的第二表面。所述方法還包括:形成從第一溝槽結構分叉的多個第二溝槽結構,其中所述第一溝槽結構的橫截面面積大于所述多個第二溝槽結構中的每個第二溝槽結構的橫截面面積。所述方法還包括:在第一表面之上形成配線層級,所述配線層級包括柵極焊盤和源極或發射極焊盤。

5、本領域技術人員將會在閱讀下面的詳細描述時并且在觀看附圖時意識到另外的特征和優點。

技術特征:

1.一種垂直功率半導體裝置(100),包括:

2.如前一權利要求所述的垂直功率半導體裝置(100),其中所述第一配線層級(104)包括銅,并且所述第二配線層級(106)包括銅。

3.如前面權利要求中任一項所述的垂直功率半導體裝置(100),還包括:屏障層,布置在所述第一配線層級(104)和所述第二配線層級(106)之間。

4.如前一權利要求所述的垂直功率半導體裝置(100),其中所述屏障層包括ti-w合金或cu-ti合金。

5.如前面兩個權利要求中任何一項所述的垂直功率半導體裝置(100),其中所述屏障層包括用于焊料化學物質的擴散屏障。

6.如前面兩個權利要求中任何一項所述的垂直功率半導體裝置(100),其中所述屏障層包括應力補償層。

7.如前面權利要求中任一項所述的垂直功率半導體裝置(100),其中所述第一配線層級(104)具有從2μm到7μm的范圍中的厚度(d1),并且所述第二配線層級(106)具有從10μm到20μm的范圍中的厚度(d2)。

8.如前面權利要求中任一項所述的垂直功率半導體裝置(100),其中所述中間介電結構(108)包括第一鈍化結構(1081),所述第一鈍化結構(1081)包括酰亞胺、氧化物或氮化物。

9.如前一權利要求所述的垂直功率半導體裝置(100),還包括:第二鈍化結構(1082),布置在所述第一鈍化結構(1081)的一部分上。

10.如前面權利要求中任一項所述的垂直功率半導體裝置(100),還包括:化學鍍結構(110),位于所述柵極焊盤(1061)上并且位于所述源極或發射極焊盤(1062)上。

11.如前一權利要求所述的垂直功率半導體裝置(100),其中所述化學鍍結構(110)包括nimop層或nip/au或nip/pd/au或nip/ag或nimop/ag層堆。

12.如前面權利要求中任一項所述的垂直功率半導體裝置(100),其中所述第一配線層級(104)還包括布置在所述第二配線層級(106)的所述柵極焊盤(1061)和所述第一表面(1031)之間的下柵極焊盤(1044),其中所述下柵極焊盤(1044)按照電氣方式連接到所述第二配線層級(106)的所述柵極焊盤(1061)。

13.如前面權利要求中任一項所述的垂直功率半導體裝置(100),其中所述第一下源極或發射極焊盤(1041)沿側向在所述第二配線層級(106)的所述柵極焊盤(1062)下方延伸,所述第一下源極或發射極焊盤(1041)通過所述中間介電結構(108)與所述第二配線層級(106)的所述柵極焊盤(1061)電絕緣。

14.一種垂直功率半導體裝置(100),包括:

15.如前一權利要求所述的垂直功率半導體裝置(100),其中所述第一溝槽結構(120)的最小側向廣度大于所述多個第二溝槽結構(122)中的每個第二溝槽結構(122)的最小側向廣度。

16.如前面兩個權利要求中任一項所述的垂直功率半導體裝置(100),其中所述第一溝槽結構(120)的垂直廣度(t1)大于所述多個第二溝槽結構(122)中的每個第二溝槽結構(122)的垂直廣度(t2)。

17.如前面三個權利要求中任一項所述的垂直功率半導體裝置(100),其中所述第一溝槽結構(120)包括柵極線材料(1201)以及布置在所述柵極線材料(1201)和所述sic半導體主體(102)之間的柵極線電介質(1202),并且所述多個第二溝槽結構(122)中的每個第二溝槽結構(122)包括柵電極材料(1221)以及布置在所述柵電極材料(1221)和所述sic半導體主體(102)之間的柵極電介質(1222);并且其中

18.如前一權利要求所述的垂直功率半導體裝置(100),其中所述柵電極材料(1221)和所述柵極線材料(1201)中的每一個包括摻雜多晶硅或金屬。

19.一種制造垂直功率半導體裝置(100)的方法,所述方法包括:

20.一種制造垂直功率半導體裝置(100)的方法,所述方法包括:

技術總結

本公開涉及包括源極或發射極焊盤的垂直功率半導體裝置,其包括:SiC半導體主體,具有第一表面和與第一表面相對的第二表面。第一配線層級被布置在第一表面之上,包括第一下源極或發射極焊盤和第二下源極或發射極焊盤。第二配線層級被布置在第一配線層級之上,包括柵極焊盤和源極或發射極焊盤。第二配線層級的源極或發射極焊盤按照電氣方式連接到第一配線層級的第一下源極或發射極焊盤和第二下源極或發射極焊盤。第一配線層級還包括:柵極線,沿側向布置在第一下源極或發射極焊盤和第二下源極或發射極焊盤之間,且沿垂直方向布置在第二配線層級的源極或發射極焊盤和第一表面之間。通過中間介電結構,柵極線與第二配線層級的源極或發射極焊盤電絕緣。

技術研發人員:R·K·喬希,C·謝弗

受保護的技術使用者:英飛凌科技股份有限公司

技術研發日:

技術公布日:2024/10/21

- 還沒有人留言評論。精彩留言會獲得點贊!