半導體裝置及其制造方法與流程

本揭露涉及一種半導體裝置及其制造方法。

背景技術:

1、電子行業已經歷對更小且更快的電子裝置的持續增大的需求,所述多個電子裝置同時能夠支持更大數目個日益錯綜且復雜的功能。因此,在半導體行業中存在制造低成本、高效能及低功率集成電路(integrated?circuit,ic)的延續趨勢。迄今為止,需求已通過按比例縮小半導體ic尺寸(例如,最小特征大小)且借此改良生產效率及減低關聯成本被大部分滿足。然而,此類縮放亦已向半導體制造工藝引入增大的復雜性。因此,半導體ic及裝置中繼續進步的實現要求半導體制造工藝及技術中的類似進步。

2、多柵極裝置已在通過增大柵極通道耦合來改良柵極控制、減小關斷狀態電流并減小短通道效應(short-channel?effect,sce)的努力中被引入。已引入的一個此類多柵極裝置是鰭片場效晶體管(fin?field-effect?transistor,finfet)。finfet自鰭片狀結構獲得其名稱,該鰭片狀結構自鰭片狀結構形成于上面的基板延伸,且鰭片狀結構用以形成fet通道。部分引入以解決與finfet相關聯的效能挑戰的另一多柵極裝置為全環繞柵極(gate-all-around,gaa)晶體管。gaa裝置自柵極結構獲得其名稱,該柵極結構完全圍繞通道延伸,從而相較于finfet提供更好靜電控制。finfet裝置及gaa裝置與互補金屬氧化物半導體(complementary?metal-oxide-semiconductor,cmos)工藝相容。另外,此類裝置的三維結構允許裝置積極地縮放,同時維持柵極控制且減輕sce。

技術實現思路

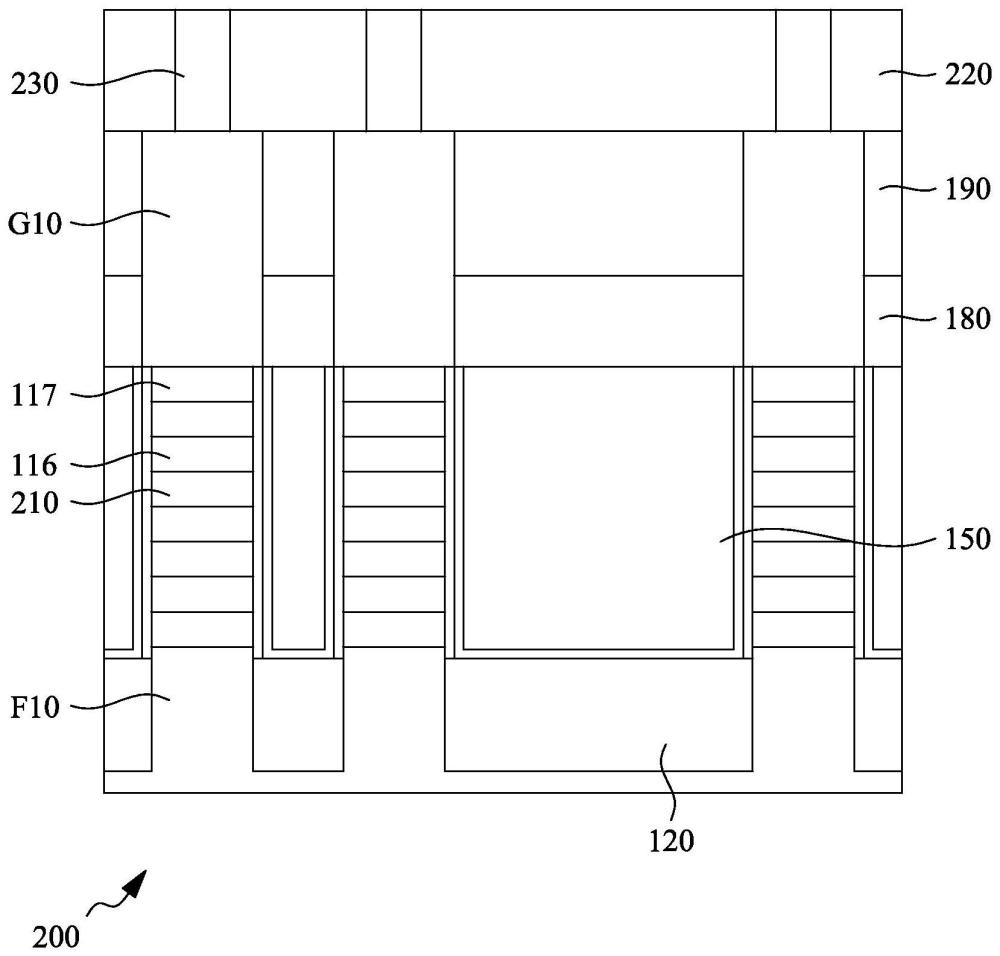

1、本揭露的一些實施方式提供一種制造半導體裝置的方法,包含以下步驟:形成由一隔離材料分離的多個鰭片結構;在所述多個鰭片結構及該隔離材料上方沉積一高k材料,其中該高k材料包括位于多個鰭片結構之間的多個下部部分及位于所述多個鰭片結構上方的一上部部分;在該高k材料上方沉積一頂蓋層;及執行一化學機械平坦化工藝以移除該頂蓋層及該高k材料的該上部部分且界定多個高k絕緣區段。

2、本揭露的一些實施方式提供一種制造半導體裝置的方法,包含以下步驟:形成一鰭片結構;形成側向相鄰于該鰭片結構的一高k隔離區,其中該高k隔離區具有一上表面;及移除該鰭片結構的一頂部層以形成具有一最上表面的該鰭片結構,該最上表面位于該高k隔離區的該上表面下方的一高度處。

3、本揭露的一些實施方式提供一種半導體裝置,包含:一半導體鰭片結構;位于該半導體鰭片結構上方的一柵極結構;及側向相鄰于該半導體鰭片結構的一氧化鉿隔離區。

技術特征:

1.一種制造半導體裝置的方法,其特征在于,包含以下步驟:

2.如權利要求1所述的方法,其特征在于,其中沉積該高k材料的步驟包含以下步驟:形成一多層結構,該多層結構包括由多個氧化鉿層及多個插入的均勻性改良層組成。

3.如權利要求1所述的方法,其特征在于,其中該化學機械平坦化工藝包含:

4.如權利要求1所述的方法,其特征在于,進一步包含以下步驟:

5.一種制造半導體裝置的方法,其特征在于,包含以下步驟:

6.如權利要求5所述的方法,其特征在于,其中一鰭片結構包含一第一鰭片材料及一第二鰭片材料的多個交替層,且其中該方法進一步包含以下步驟:

7.一種半導體裝置,其特征在于,包含:

8.如權利要求7所述的半導體裝置,其特征在于,其中:

9.如權利要求7所述的半導體裝置,其特征在于,其中:

10.如權利要求7所述的半導體裝置,其特征在于,其中:

技術總結

本揭露提供半導體裝置及其制造方法。一種例示性方法包括:形成由一隔離材料分離的多個鰭片結構;在所述多個鰭片結構及隔離材料上方沉積一高k材料,其中該高k材料包括位于多個鰭片結構之間的多個下部部分及位于所述多個鰭片結構上方的一上部部分;在該高k材料上方沉積一地形改良頂蓋層;執行一化學機械平坦化(CMP)工藝以移除該頂蓋層及該高k材料的該上部部分且界定多個高k絕緣區段。

技術研發人員:黃罡,卓登明,潘婉君,孫旭昌

受保護的技術使用者:臺灣積體電路制造股份有限公司

技術研發日:

技術公布日:2024/10/21

- 還沒有人留言評論。精彩留言會獲得點贊!