半導體封裝構造及其芯片的制作方法

本發明是關于一種半導體封裝構造及其芯片,尤其是一種避免接合于凸塊的接腳發生偏移或錯位接合的半導體封裝構造及其芯片。

背景技術:

1、現有習知的半導體封裝構造是借由熱壓合工藝將芯片的多個凸塊接合至基板的多個接腳,以使該芯片與該基板電性連接,然由于芯片的微形化趨勢,使得該芯片的所述多個凸塊間的間距縮小,必要時,所述多個凸塊更形成了多排排列的態樣,以利電性連接該基板,然而,當以單排或多排排列的所述多個凸塊接合所述多個接腳時,由于工藝環境溫度影響,若該基板發生變形,會造成接合在所述多個凸塊的所述多個接腳發生偏移,例如接合于該芯片中間位置的接腳或鄰近該芯片短側邊的接腳,因該基板收縮或翹曲所產生的應變及應力而發生偏移,進而使接合于該芯片的所述多個凸塊上的所述多個接腳脫離所述多個凸塊或發生錯位接合的問題。

技術實現思路

1、本發明的主要目的是在提供一種半導體封裝構造及其芯片,借由不同長度的凸塊設計,以增加凸塊對接腳的接合力,以避免接合在凸塊上的接腳發生偏移,而發生接腳脫離凸塊或錯位接合的問題。

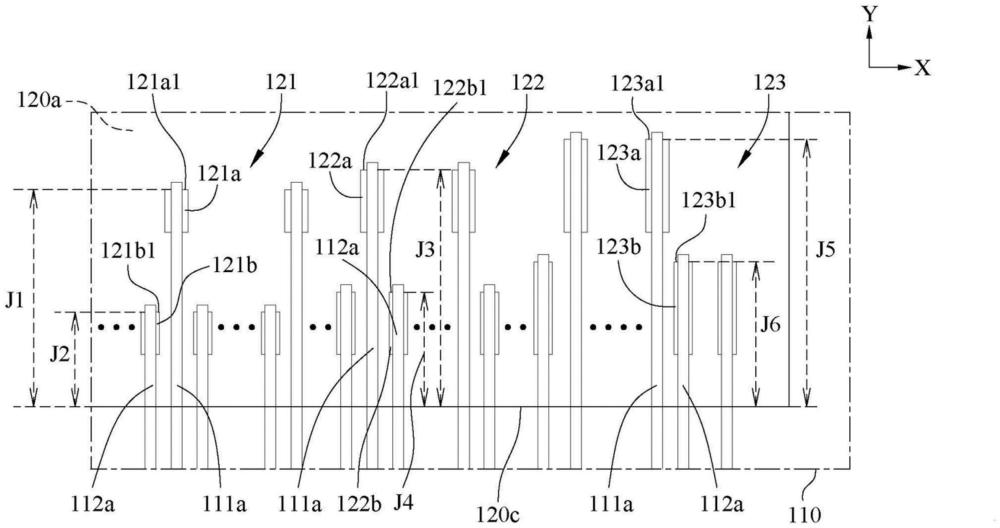

2、本發明的一種半導體封裝構造,包含可撓電路基板及芯片,該可撓電路基板具有芯片接合區、多個第一線路及多個第二線路,相鄰的該第一線路之間具有至少一個該第二線路,各該第一線路具有第一接腳,各該第二線路具有第二接腳,各該第一接腳及各該第二接腳位于該芯片接合區,該芯片具有表面、第一凸塊群及至少一個第二凸塊群,沿著第一軸線,該表面具有第一區及至少一個第二區,該第一凸塊群設置于該第一區,該第二凸塊群設置于該第二區,該第一凸塊群包含多個第一內凸塊及多個第一外凸塊,該第二凸塊群包含多個第二內凸塊及多個第二外凸塊,沿著與該第一軸線相交的第二軸線,所述多個第一外凸塊較所述多個第一內凸塊鄰近該表面的長側邊,所述多個第二外凸塊較所述多個第二內凸塊鄰近該長側邊,沿著該第二軸線,各該第一內凸塊具有第一長度,各該第一外凸塊具有第二長度,各該第二內凸塊具有第三長度,各該第二外凸塊具有第四長度,該第三長度大于該第一長度,該第四長度大于該第二長度,所述多個第一接腳分別接合于所述多個第一內凸塊及所述多個第二內凸塊,所述多個第二接腳分別接合于所述多個第一外凸塊及所述多個第二外凸塊,各該第二內凸塊與各該第一接腳的接合面積大于各該第一內凸塊與各該第一接腳的接合面積,各該第二外凸塊與各該第二接腳的接合面積大于各該第一外凸塊與各該第二接腳的接合面積。

3、本發明的一種半導體封裝構造的芯片,其包含表面、第一凸塊群及至少一個第二凸塊群,沿著第一軸線,該表面具有第一區及至少一個第二區,該第一凸塊群設置于該第一區,該第二凸塊群設置于該第二區,該第一凸塊群包含多個第一內凸塊及多個第一外凸塊,該第二凸塊群包含多個第二內凸塊及多個第二外凸塊,沿著與該第一軸線相交的第二軸線,所述多個第一外凸塊較所述多個第一內凸塊鄰近該表面的長側邊,所述多個第二外凸塊較所述多個第二內凸塊鄰近該長側邊,其特征在于:沿著該第二軸線,各該第一內凸塊具有第一長度,各該第一外凸塊具有第二長度,各該第二內凸塊具有第三長度,各該第二外凸塊具有第四長度,該第三長度大于該第一長度,該第四長度大于該第二長度。

4、本發明的一種半導體封裝構造的芯片,其包含多個第一凸塊及多個第二凸塊,沿著第一軸線,該表面具有第一區及至少一個第二區,所述多個第一凸塊設置于表面的第一區,所述多個第二凸塊設置于該表面的第二區,其特征在于:沿著與該第一軸線相交的第二軸線,各該第二凸塊的長度大于各該第一凸塊的長度。

5、本發明借由該第二凸塊群及/或該第三凸塊群的凸塊長度大于該第一凸塊群的凸塊長度,以增加該第二凸塊群及/或該第三凸塊群對所述多個第一接腳及/或所述多個第二接腳的接合力,以避免接合于該第二凸塊群及/或該第三凸塊群的所述多個第一接腳及/或所述多個第二接腳發生偏移而脫離所述多個第二凸塊或發生錯位接合的問題。

技術特征:

1.一種半導體封裝構造,其特征在于,包含:

2.根據權利要求1所述的半導體封裝構造,其特征在于,該第二長度不大于該第三長度,該第四長度大于該第一長度,各該第二外凸塊與各該第二接腳的接合面積大于各該第一內凸塊與各該第一接腳的接合面積。

3.根據權利要求2所述的半導體封裝構造,其特征在于,該第二長度小于該第三長度,各該第二內凸塊與各該第一接腳的接合面積大于各該第一外凸塊與各該第二接腳的接合面積。

4.根據權利要求1所述的半導體封裝構造,其特征在于,沿著該第二軸線,接合于各該第一內凸塊的各該第一接腳具有由該長側邊至各該第一內凸塊的內端的第一腳長,接合于各該第二內凸塊的各該第一接腳具有由該長側邊至各該第二內凸塊的內端的第三腳長,該第三腳長大于該第一腳長。

5.根據權利要求4所述的半導體封裝構造,其特征在于,沿著該第二軸線,接合于各該第一外凸塊的各該第二接腳具有由該長側邊至各該第一外凸塊的內端的第二腳長,接合于各該第二外凸塊的各該第二接腳具有由該長側邊至各該第二外凸塊的內端的第四腳長,該第二腳長大于該第二腳長。

6.根據權利要求1所述的半導體封裝構造,其特征在于,沿著該第一軸線,該第二區較該第一區鄰近該表面的短側邊,所述多個第二內凸塊較所述多個第一內凸塊鄰近該短側邊,所述多個第二外凸塊較所述多個第一外凸塊鄰近該短側邊。

7.根據權利要求1所述的半導體封裝構造,其特征在于,沿著該第一軸線,基準線通過至少一個該第一內凸塊,沿著該第二軸線,各該第一外凸塊的內端至該基準線之間具有第一距離,各該第二外凸塊的內端至該基準線之間具有第二距離,該第一距離大于該第二距離。

8.根據權利要求5所述的半導體封裝構造,其特征在于,該芯片另具有至少一個第三凸塊群,沿著該第一軸線,該表面具有至少一個第三區,該第二區位于第一區與該第三區之間,該第三凸塊群設置于該第三區,沿著該第一軸線,該第二凸塊群位于該第一凸塊群與該第三凸塊群之間,該第三凸塊群包含多個第三內凸塊及多個第三外凸塊,沿著該第二軸線,所述多個第三外凸塊較所述多個第三內凸塊鄰近該長側邊,沿著該第一軸線,所述多個第二內凸塊位于所述多個第三內凸塊與所述多個第一內凸塊之間,所述多個第二外凸塊位于所述多個第三外凸塊與所述多個第一外凸塊之間,沿著該第二軸線,各該第三內凸塊具有第五長度,各該第三外凸塊具有第六長度,該第五長度大于該第三長度,該第六長度大于該第四長度,所述多個第一接腳分別接合于所述多個第三內凸塊,所述多個第二接腳分別接合于所述多個第三外凸塊,各該第三內凸塊與各該第一接腳的接合面積大于各該第二內凸塊與各該第一接腳的接合面積,各該第三外凸塊與各該第二接腳的接合面積大于各該第二外凸塊與各該第二接腳的接合面積。

9.根據權利要求8所述的半導體封裝構造,其特征在于,該第四長度不大于該第五長度,該第六長度大于該第三長度,各該第三外凸塊與各該第二接腳的接合面積大于各該第二內凸塊與各該第一接腳的接合面積。

10.根據權利要求8所述的半導體封裝構造,其特征在于,該第四長度小于該第五長度,各該第三內凸塊與各該第一接腳的接合面積大于各該第二外凸塊與各該第二接腳的接合面積。

11.根據權利要求8所述的半導體封裝構造,其特征在于,沿著該第二軸線,接合于各該第三內凸塊的各該第一接腳具有由該長側邊至各該第三內凸塊的內端的第五腳長,該第五腳長大于該第三腳長,接合于各該第三外凸塊的各該第二接腳具有由該長側邊至各該第三外凸塊的內端的第六腳長,該第六腳長大于該第四腳長。

12.根據權利要求8所述的半導體封裝構造,其特征在于,沿著該第二軸線,基準線通過至少一個該第一內凸塊,沿著該第二軸線,各該第一外凸塊的內端至該基準線之間具有第一距離,各該第二外凸塊的內端至該基準線之間具有第二距離,各該第三外凸塊的內端至該基準線之間具有第三距離,該第一距離大于該第二距離,該第二距離大于該第三距離。

13.根據權利要求8所述的半導體封裝構造,其特征在于,沿著該第一軸線,該第一區的寬度占該芯片的寬度的40%至80%,各該第二區的寬度占該芯片的該寬度的5%至15%,各該第三區的寬度占該芯片的該寬度的5%至15%。

14.一種半導體封裝構造的芯片,其特征在于,其包含表面、第一凸塊群及至少一個第二凸塊群,沿著第一軸線,該表面具有第一區及至少一個第二區,該第一凸塊群設置于該第一區,該第二凸塊群設置于該第二區,該第一凸塊群包含多個第一內凸塊及多個第一外凸塊,該第二凸塊群包含多個第二內凸塊及多個第二外凸塊,沿著與該第一軸線相交的第二軸線,所述多個第一外凸塊較所述多個第一內凸塊鄰近該表面的長側邊,所述多個第二外凸塊較所述多個第二內凸塊鄰近該長側邊,其特征在于:沿著該第二軸線,各該第一內凸塊具有第一長度,各該第一外凸塊具有第二長度,各該第二內凸塊具有第三長度,各該第二外凸塊具有第四長度,該第三長度大于該第一長度,該第四長度大于該第二長度。

15.根據權利要求14所述的半導體封裝構造的芯片,其特征在于,該第二長度不大于該第三長度,該第四長度大于該第一長度。

16.根據權利要求15所述的半導體封裝構造的芯片,其特征在于,該第二長度小于該第三長度。

17.根據權利要求14所述的半導體封裝構造的芯片,其特征在于,沿著該第一軸線,各該第一內凸塊具有第一寬度,各該第一外凸塊具有第二寬度,該第一寬度大于該第二寬度。

18.根據權利要求14所述的半導體封裝構造的芯片,其特征在于,沿著該第一軸線,基準線通過至少一個該第一內凸塊,沿著該第二軸線,各該第一外凸塊的內端至該基準線之間具有第一距離,各該第二外凸塊的內端至該基準線之間具有第二距離,該第一距離大于該第二距離。

19.根據權利要求14所述的半導體封裝構造的芯片,其特征在于,該芯片另具有至少一個第三凸塊群,沿著該第一軸線,該表面具有至少一個第三區,該第二區位于第一區與該第三區之間,該第三凸塊群設置于該第三區,沿著該第一軸線,該第二凸塊群位于該第一凸塊群與該第三凸塊群之間,該第三凸塊群包含多個第三內凸塊及多個第三外凸塊,沿著該第二軸線,所述多個第三外凸塊較所述多個第三內凸塊鄰近該長側邊,沿著該第一軸線,所述多個第二內凸塊位于所述多個第三內凸塊與所述多個第一內凸塊之間,所述多個第二外凸塊位于所述多個第三外凸塊與所述多個第一外凸塊之間,沿著該第二軸線,各該第三內凸塊具有第五長度,各該第三外凸塊具有第六長度,該第五長度大于該第三長度,該第六長度大于該第四長度。

20.一種半導體封裝構造的芯片,其特征在于,其包含多個第一凸塊及多個第二凸塊,沿著第一軸線,該表面具有第一區及至少一個第二區,所述多個第一凸塊設置于表面的第一區,所述多個第二凸塊設置于該表面的第二區,其特征在于:沿著與該第一軸線相交的第二軸線,各該第二凸塊的長度大于各該第一凸塊的長度。

技術總結

本發明是一種半導體封裝構造及其芯片。該半導體封裝構造包含可撓電路基板及芯片,該可撓電路基板具有多個接腳,該芯片具有第一凸塊群及至少一個第二凸塊群,該第一凸塊群包含多個第一凸塊,該第二凸塊群包含多個第二凸塊,所述多個接腳分別接合于所述多個第一凸塊及所述多個第二凸塊,借由各該第二凸塊的長度大于各該第一凸塊的長度,以增加該第二凸塊群對所述多個接腳的接合力,以避免所述多個接腳發生偏移而脫離所述多個第二凸塊或錯位接合的問題。

技術研發人員:吳偉新,張谷榜,葉峻嘉

受保護的技術使用者:頎邦科技股份有限公司

技術研發日:

技術公布日:2024/10/21

- 還沒有人留言評論。精彩留言會獲得點贊!