列選通信號控制電路的制作方法

本發明涉及半導體芯片存儲,具體地說,特別涉及一種消除工藝、電壓和溫度對列選通脈沖寬度的影響,使其按照系統工作頻率改變的列選通信號控制電路。

背景技術:

1、計算機內的數據以二進制1或者0來表示,存儲器存儲數據的方式為,對于存儲陣列中的一個存儲單元,當其中的電容被感應到存在電荷時,即可用以表示二進制的1,反之,則用以表示二進制的0。在此基礎上,對存儲器的讀操作,本質上也即感應和判斷存儲陣列中某個存儲單元的電容中是否存在電荷,又或者是感應該電容與位線之間的電荷差,而存儲器的寫操作,是通過刷新電路的方式重新對存儲單元的陣列進行充電和放電。

2、存儲設備中包含數量眾多的存儲單元,這些存儲單元按照行列分布構成存儲陣列。為了區分和表示這些存儲單元,系統為存儲陣列配置了行地址和列地址,行列地址分別指向一次數據讀寫操作所訪問的行或者列,同時,也就用行地址和列地址唯一指向了陣列中的一個存儲單元。

3、一次讀寫操作的開始,需要首先激活行地址和列地址。行地址用于選擇讀寫操作的行,列地址用于選擇讀寫操作對應的列,當列地址激活后,位線(bit?line)與存儲陣列的數據輸入輸出連通,并共享兩者之間的電荷。一次讀寫操作完畢后,再對存儲陣列中的數據進行刷新,以等待下一次數據讀寫操作。

4、按照如上所述的存儲陣列結構和數據讀寫方式,容易理解的是,為保證計算機中的數據讀寫的準確,應當總是要求數據與地址之間實現映射,也即,地址信號和數據信號始終保持同步。如前所述,列地址激活時,位線才能與存儲陣列連通并共享電荷,據此,列選通信號csl的脈沖寬度(也即,選通信號的激活或者開啟時間)就顯得尤為重要,該脈沖寬度、信號激活時間應當與數據信號保持對應。

5、現有技術下,列選通信號的脈沖寬度普遍采用延遲電路來控制。延遲電路的作用,是為系統實現固定的延遲時間,通過延遲電路輸出的固定時間延遲信號,列選通信號的脈沖寬度被維持在相同的開啟時長和開啟間隔內。然而,存儲器(例如dram)往往又需要能夠支持在不同的工作頻率下運行,理論上,系統會要求在不同工作頻率下,選通信號的開啟時間和時長仍然按照延遲電路輸出的延遲時間保持一致。但同時,另一個方面的問題是,實現延遲電路的元器件(例如偶數個反向器組成的延遲電路),在執行過程中易受工藝、電壓和溫度的變化影響,這會導致延遲電路在不同pvt環境下輸出的延遲時間并不總是相同的,而延遲電路輸出的延遲時間的波動,也即直接影響選通信號的開啟和維持時長,最終致使選通地址和數據之間的失配。

6、因此,應當對吸納有技術下列選通信號的控制方式進行改進,以解決現有技術的上述技術問題。

技術實現思路

1、有鑒于此,本發明提供了一種,至少解決上述問題之一。

2、為解決以上技術問題,本發明提供的一種列選通信號控制電路,該電路包括至少一個觸發器,該觸發器以所述讀寫命令為數據輸入;時鐘信號,該時鐘信號為應對系統頻率而呈現變化的控制信號,所述時鐘信號作為使能信號并被接至所述觸發器的使能端,其中,所述觸發器根據所述時鐘信號輸出一路選通開啟信號,該選通開啟信號被接至所述列解碼器,以使得所述列解碼器根據所述選通開啟信號輸出列選通信號。

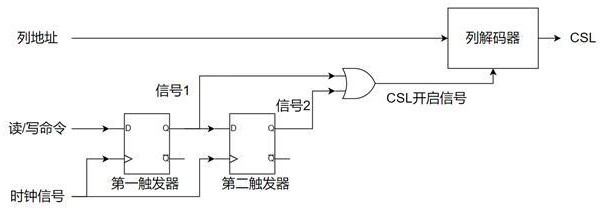

3、作為本方案較佳實施例的一種更優選的,一路列地址信號和一路讀寫命令信號,并用于通過列解碼器輸出列選通信號,其中,該控制電路還包括至少兩個觸發器,前級所述觸發器以所述讀寫命令為數據輸入,且前級觸發器的輸出作為后級觸發器的輸入,其中,兩觸發器分別輸出兩路信號,定義為第一信號和第二信號,所述第一信號和第二信號被接至邏輯門『或』,以得到第一控制信號,該第一控制信號被接至列解碼器,以使得所述列解碼器根據一路所述第一控制信號輸出列選通信號。

4、作為本方案的一種較優選地,還包括延遲比較電路,該延遲比較電路的輸出作為所述列解碼器的輸入,所述延遲比較電路由一路延遲電路和一路比較電路組合以形成,所述延遲電路對所述第一控制信號進行延遲,以已得到第二控制信號,所述比較電路對所述第一控制信號和第二控制信號進行比較,以輸出脈沖寬度小于等于所述第一控制信號的第三控制信號,其中,所述比較電路包括一邏輯門『與』,該邏輯門『與』的兩路輸入分別為所述第一控制信號和所述第一控制信號被延遲后的第二控制信號。

5、作為本方案的進一步優選地,所述延遲電路包括第一延遲單元和第二延遲單元,以及配置在所述第一延遲單元的輸出和第二延遲單元的輸入之間的邏輯『與非』門,所述第一延遲單元的輸入為所述第一控制信號,第一延遲單元對所述第一控制信號按照預設的延遲時間進行延遲;所述邏輯『與非』門的一路輸入為所述第一控制信號,另一路輸入為所述第一延遲單元的輸入,所述邏輯『與非』門輸出第一延遲信號,該第一延遲信號作為所述第二延遲單元的輸入,第二延遲單元的輸出為所述第二控制信號。

6、相較于現有技術,實施本發明所取得的有益技術效果為:

7、本方案首先采用計數器計數的方式,取代現有的延遲電路方式,以生成固定開啟時長的列選通信號,尤其是,輸出的最終控制信號與工作頻率相關,避免了元器件因受工作環境變化影響,導致的列選通信號開啟時間變化帶來的一系列問題。同時,為解決系統低頻工作時,因感應放大器長時間開啟帶來的功耗問題,引入了延遲比較電路,縮小控制信號的脈沖寬度。

技術特征:

1.一種列選通信號控制電路,該電路包括一路列地址信號和一路讀寫命令信號,并用于通過列解碼器輸出列選通信號,其中,該控制電路還包括

2.根據權利要求1所述的列選通信號控制電路,其中,該控制電路包括:

3.根據權利要求2所述的列選通信號控制電路,其中,還包括延遲比較電路,該延遲比較電路的輸出作為所述列解碼器的輸入,所述延遲比較電路由一路延遲電路和一路比較電路組合以形成,所述延遲電路對所述第一控制信號進行延遲,以得到第二控制信號,所述比較電路對所述第一控制信號和第二控制信號進行比較,以輸出脈沖寬度小于等于所述第一控制信號的第三控制信號,其中,所述比較電路包括一邏輯門『與』,該邏輯門『與』的兩路輸入分別為所述第一控制信號和所述第一控制信號被延遲后的第二控制信號。

4.根據權利要求3所述的列選通信號控制電路,其中,所述延遲電路包括第一延遲單元和第二延遲單元,以及配置在所述第一延遲單元的輸出和第二延遲單元的輸入之間的邏輯『與非』門,

技術總結

提供一種列選通信號控制電路,該電路包括多個通過時鐘信號使能的觸發器,并輸出一路僅和系統工作頻率相關的控制信號,再通過延遲比較電路,將觸發器輸出的控制信號,與經延遲后的控制信號進行比較,根據邏輯『與』門的輸出,得到脈沖寬度小于等于原控制信號的輸出信號,以在系統低頻工作工況下,縮小列選通信號的脈沖寬度,這樣,在消除工藝、電壓和溫度對列選通信號開啟時間造成的影響的同時,降低系統低頻工作時,感應放大器持續工作帶來的功耗。

技術研發人員:馬駿梁

受保護的技術使用者:浙江力積存儲科技有限公司

技術研發日:

技術公布日:2024/12/23

- 還沒有人留言評論。精彩留言會獲得點贊!