一種可配置電平高低有效且可切換輸入輸出的GPIO電路的制作方法

本發明涉及集成電路設計與微電子技術的領域,尤其涉及一種可配置電平高低有效且可切換輸入輸出的gpio電路。

背景技術:

1、在現代數字系統中,通用輸入/輸出(gpio)接口是不可或缺的一部分,它們通常用于設備間的數據傳輸和控制信號交互。然而,現有的gpio接口往往固定其電平有效性和輸入/輸出模式,不能根據實際應用場景進行靈活配置,這在一定程度上限制了系統的兼容性及靈活性。

技術實現思路

1、本發明旨在解決現有技術的不足,而提供一種可配置電平高低有效且可切換輸入輸出的gpio電路。

2、本發明為實現上述目的,采用以下技術方案:

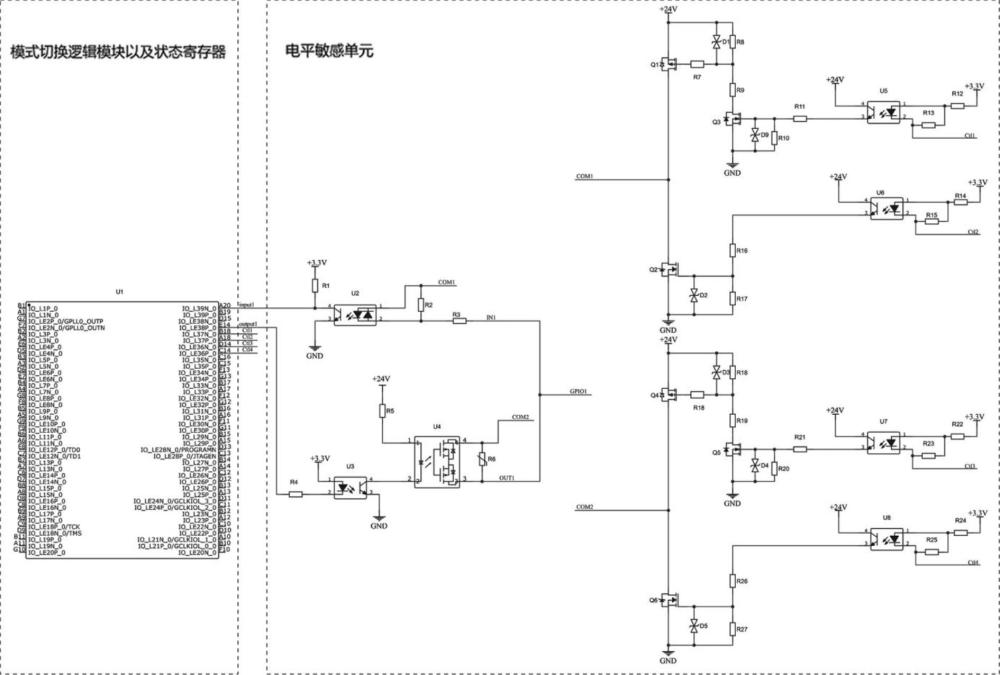

3、一種可配置電平高低有效且可切換輸入輸出的gpio電路,包括模式切換邏輯模塊以及狀態寄存器、電平敏感單元;模式切換邏輯模塊依據狀態寄存器中的配置信息決定gpio的工作模式;狀態寄存器存儲存儲對gpio工作方式的設定;電平敏感單元負責檢測并轉換引腳上的高低電平信號。

4、gpio工作方式的設定包括電平有效性、輸入/輸出模式。

5、模式切換邏輯模塊以及狀態寄存器的u1的a20為輸入端引腳,u1的e14為輸出端引腳;電平敏感單元包括輸入部分電路和輸出部分電路:輸入部分電路包括外部輸信號檢測部分和com1電平配置部分;輸出部分電路包括輸出端口控制部分和com2電平配置部分。

6、輸入部分電路的外部輸信號檢測部分具體電路如下:

7、u1的a20引腳接光耦u2的4腳,u2的1腳與com1連接,u2的2腳串接限流電阻r3與對外端口gpio1相連接,u2的1腳、2腳之間連接有限流電阻r2,u2的3腳與gnd相連接,u2的4腳通過限流電阻r1上拉至3.3v電平。

8、輸入部分電路的com1電平配置部分具體電路如下:

9、u1的b18引腳接光耦u5的2腳,u5的1腳通過限流電阻r12接dc3.3v,u5的1腳與2腳之間連接有電阻r13,u5的4腳接dc24v電平,u5的3腳通過限流電阻r11接q3的柵極,q3的柵極與源極之間連接保護二極管d9和分流保護電阻r10,q3的源極與gnd相連接,q3的漏極、q1的柵極之間串接限流電阻r9和限流電阻r7,q1的柵極串接限流電阻r7后與源極之間連接保護二極管d1和限流電阻r8,q1的源極與dc24v電平相連接,q1的漏極為com1;

10、u1的a18引腳接光耦u6的2腳,u6的1腳通過限流電阻r14接dc3.3v,u6的1腳與2腳之間連接有電阻r15,u6的4腳接dc24v電平,u6的3腳通過限流電阻r16接q2的柵極,q2的柵極與源極之間連接保護二極管d2和分流保護電阻r17,q2的源極與gnd相連接,q2的漏極為com1。

11、輸出部分電路的輸出端口控制部分具體電路如下:

12、u1的e14引腳串接限流電阻r4與光耦u3的2腳連接,u3的1腳與dc3.3v連接,u3的3腳與gnd相連接,u3的4腳與光耦u4的2腳連接,u4的1腳通過限流電阻r5連接至dc24v,u4的3腳、4腳之間連接有變阻r6,u4的3腳為gpio1,u4的4腳為com2。

13、輸出部分電路的com2電平配置部分具體電路如下:

14、u1的d14引腳接光耦u7的2腳,u7的1腳通過限流電阻r22接dc3.3v,u7的1腳、2腳之間連接有電阻r23,u7的4腳接dc24v電平,u7的3腳通過限流電阻r21接q5的柵極,q5的柵極與源極之間連接保護二極管d4和分流保護電阻r20,q5的源極與gnd相連接,q5的漏極、q4的柵極之間串接限流電阻r18、限流電阻r19,q4的柵極串接限流電阻r18后與源極之間連接保護二極管d3和另外一個限流電阻r18,q4的源極與dc24v電平相連接,q4的漏極為com2;

15、u1的c14引腳接光耦u8的2腳,u8的1腳通過限流電阻r24接dc3.3v,u8的1腳、2腳之間連接有電阻r25,u8的4腳接dc24v電平,u8的3腳通過限流電阻r26接q6的柵極,q6的柵極與源極之間連接保護二極管d5和分流保護電阻r27,q6的源極與gnd相連接,q6的漏極為com2。

16、本發明的有益效果是:本發明能夠通過內部寄存器設置,可以將gpio引腳配置為高電平有效或低電平有效,以滿足不同協議或硬件設備的需求;通過軟件指令或硬件觸發機制,能夠在輸入模式和輸出模式之間實時切換;支持在系統運行過程中隨時修改電平有效性和輸入輸出模式,無需重啟系統,顯著提高了系統響應速度和資源利用率。

技術特征:

1.一種可配置電平高低有效且可切換輸入輸出的gpio電路,其特征在于,包括模式切換邏輯模塊以及狀態寄存器、電平敏感單元;模式切換邏輯模塊依據狀態寄存器中的配置信息決定gpio的工作模式;狀態寄存器存儲存儲對gpio工作方式的設定;電平敏感單元負責檢測并轉換引腳上的高低電平信號。

2.根據權利要求1所述的一種可配置電平高低有效且可切換輸入輸出的gpio電路,其特征在于,gpio工作方式的設定包括電平有效性、輸入/輸出模式。

3.根據權利要求2所述的一種可配置電平高低有效且可切換輸入輸出的gpio電路,其特征在于,模式切換邏輯模塊以及狀態寄存器的u1的a20為輸入端引腳,u1的e14為輸出端引腳;電平敏感單元包括輸入部分電路和輸出部分電路:輸入部分電路包括外部輸信號檢測部分和com1電平配置部分;輸出部分電路包括輸出端口控制部分和com2電平配置部分。

4.根據權利要求3所述的一種可配置電平高低有效且可切換輸入輸出的gpio電路,其特征在于,輸入部分電路的外部輸信號檢測部分具體電路如下:

5.根據權利要求4所述的一種可配置電平高低有效且可切換輸入輸出的gpio電路,其特征在于,輸入部分電路的com1電平配置部分具體電路如下:

6.根據權利要求5所述的一種可配置電平高低有效且可切換輸入輸出的gpio電路,其特征在于,輸出部分電路的輸出端口控制部分具體電路如下:

7.根據權利要求6所述的一種可配置電平高低有效且可切換輸入輸出的gpio電路,其特征在于,輸出部分電路的com2電平配置部分具體電路如下:

技術總結

本發明是一種可配置電平高低有效且可切換輸入輸出的GPIO電路,包括模式切換邏輯模塊以及狀態寄存器、電平敏感單元;模式切換邏輯模塊依據狀態寄存器中的配置信息決定GPIO的工作模式;狀態寄存器存儲存儲對GPIO工作方式的設定;電平敏感單元負責檢測并轉換引腳上的高低電平信號。本發明能夠通過內部寄存器設置,可以將GPIO引腳配置為高電平有效或低電平有效,以滿足不同協議或硬件設備的需求;通過軟件指令或硬件觸發機制,能夠在輸入模式和輸出模式之間實時切換;支持在系統運行過程中隨時修改電平有效性和輸入輸出模式,無需重啟系統,顯著提高了系統響應速度和資源利用率。

技術研發人員:關騰騰,劉兵,孫廣澤

受保護的技術使用者:天津新松智能科技有限公司

技術研發日:

技術公布日:2024/10/14

- 還沒有人留言評論。精彩留言會獲得點贊!