一種日志傳輸方法、裝置、設備及存儲介質與流程

本發明涉及多核處理器,尤其涉及一種日志傳輸方法、裝置、設備及存儲介質。

背景技術:

1、目前,傳統的微控制單元(microcontroller?unit,mcu)日志傳輸系統比較常見的日志傳輸方式是,實時的將mcu輸出的日志通過對應通道(例如以太網)傳輸到系統芯片進行存儲,或傳輸到計算機端進行調試。

2、然而,對于多核的mcu,每個核都是獨立運行的,每個核的負載通常不同,每個核在空閑時會輸出自己本核產生的日志。在日志量過大的場景下,會導致某些先觸發的日志,后被輸出,從而對后續的日志分析造成負面影響。

技術實現思路

1、本發明提供了一種日志傳輸方法、裝置、設備及存儲介質,以解決多核mcu的日志輸出混亂的問題。

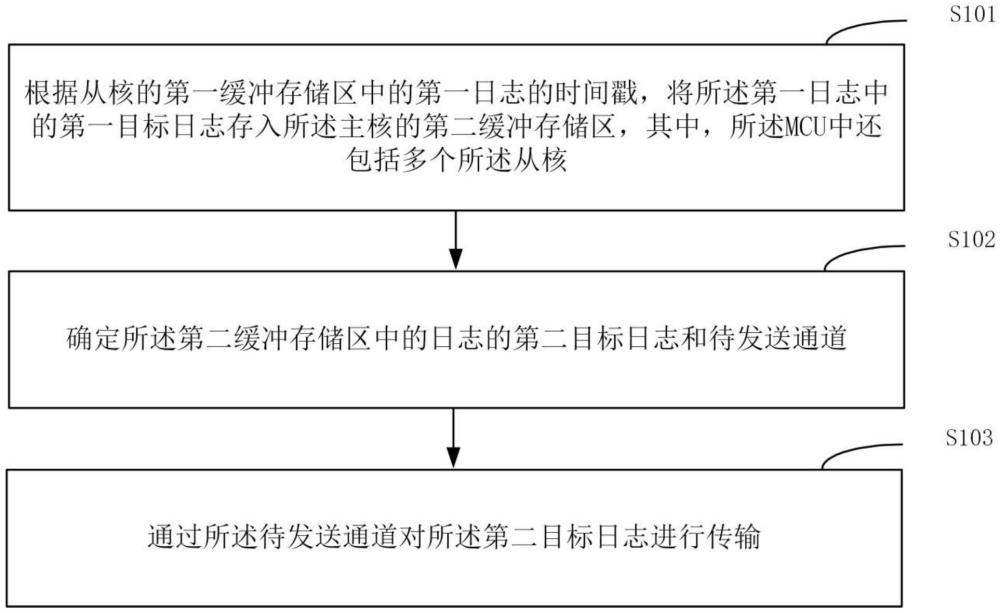

2、第一方面,本發明提供了一種日志傳輸方法,應用于微控制單元mcu中的主核,該方法包括:

3、根據從核的第一緩沖存儲區中的第一日志的時間戳,將所述第一日志中的第一目標日志存入所述主核的第二緩沖存儲區,其中,所述mcu中還包括多個所述從核;

4、確定所述第二緩沖存儲區中的日志的第二目標日志和待發送通道;

5、通過所述待發送通道對所述第二目標日志進行傳輸。

6、第二方面,本發明提供了一種日志傳輸裝置,應用于微控制單元mcu中的主核,該裝置包括:

7、日志存儲模塊,用于根據從核的第一緩沖存儲區中的第一日志的時間戳,將所述第一日志中的第一目標日志存入所述主核的第二緩沖存儲區,其中,所述mcu中還包括多個所述從核;

8、目標日志和通道確定模塊,用于確定所述第二緩沖存儲區中的日志的第二目標日志和待發送通道;

9、日志傳輸模塊,用于通過所述待發送通道對所述第二目標日志進行傳輸。

10、第三方面,本發明提供了一種電子設備,該電子設備包括微控制單元;

11、所述微控制單元中包括目標主核和多個目標從核;

12、其中,所述目標主核能夠執行上述第一方面中所述的日志傳輸方法。

13、第四方面,本發明提供了一種計算機可讀存儲介質,該計算機可讀存儲介質存儲有計算機指令,計算機指令用于使處理器執行時實現上述第一方面的日志傳輸方法。

14、本發明提供的日志傳輸方案,應用于微控制單元mcu中的主核,主核根據從核的第一緩沖存儲區中的第一日志的時間戳,將所述第一日志中的第一目標日志存入所述主核的第二緩沖存儲區,其中,所述mcu中還包括多個所述從核,確定所述第二緩沖存儲區中的日志的第二目標日志和待發送通道,通過所述待發送通道對所述第二目標日志進行傳輸。通過采用上述技術方案,劃分了多核的mcu中的主核和從核,根據從核的緩沖存儲區中的日志的時間戳,可以實現有序的將從核中的日志的存儲至主核的緩沖存儲區,并通過待發送通道實現對待發送日志的有序傳輸,有利于后續對日志的分析。

15、應當理解,本部分所描述的內容并非旨在標識本發明的關鍵或重要特征,也不用于限制本發明的范圍。本發明的其它特征將通過以下的說明書而變得容易理解。

技術特征:

1.一種日志傳輸方法,其特征在于,應用于微控制單元mcu中的主核,所述方法包括:

2.根據權利要求1所述的方法,其特征在于,所述根據從核的第一緩沖存儲區中的第一日志的時間戳,將所述第一日志中的第一目標日志存入所述主核的第二緩沖存儲區,包括:

3.根據權利要求2所述的方法,其特征在于,所述第二緩沖存儲區中的日志按照時間戳的先后順序排列。

4.根據權利要求1所述的方法,其特征在于,所述確定所述第二緩沖存儲區中的日志的第二目標日志和待發送通道,包括:

5.根據權利要求1-4中任一項所述的方法,其特征在于,還包括:

6.根據權利要求1所述的方法,其特征在于,所述通過所述待發送通道對所述第二目標日志進行傳輸,包括:

7.根據權利要求1所述的方法,其特征在于,所述通過所述待發送通道對所述第二目標日志進行傳輸,包括:

8.一種日志傳輸裝置,其特征在于,應用于微控制單元mcu中的主核,所述裝置包括:

9.一種電子設備,其特征在于,所述電子設備包括微控制單元;

10.一種計算機可讀存儲介質,其特征在于,所述計算機可讀存儲介質存儲有計算機指令,所述計算機指令用于使處理器執行時實現權利要求1-7中任一項所述的日志傳輸方法。

技術總結

本發明公開了一種日志傳輸方法、裝置、設備及存儲介質。該方法應用于微控制單元MCU中的主核,包括:根據從核的第一緩沖存儲區中的第一日志的時間戳,將所述第一日志中的第一目標日志存入所述主核的第二緩沖存儲區,其中,所述MCU中還包括多個所述從核,確定所述第二緩沖存儲區中的日志的第二目標日志和待發送通道,通過所述待發送通道對所述第二目標日志進行傳輸。本發明實施例的技術方案,劃分了多核MCU中的主核和從核,根據從核的緩沖存儲區中的日志的時間戳,實現了有序的將從核中的日志的存儲至主核的緩沖存儲區,并通過待發送通道實現對待發送日志的有序傳輸,有利于后續對日志的分析。

技術研發人員:朱奎泉,馬峰,張朝松

受保護的技術使用者:成都市卡蛙科技有限公司

技術研發日:

技術公布日:2024/10/21

- 還沒有人留言評論。精彩留言會獲得點贊!