具有分支DFE復位路徑的數據輸入緩沖器的制作方法

本公開的實施例大體上涉及用于存儲器裝置的輸入緩沖器及判決反饋均衡器(dfe)領域。更具體來說,本公開的實施例涉及復位dfe的抽頭及分離輸入緩沖器中的數據路徑及抽頭路徑的分支dfe復位路徑。

背景技術:

1、半導體裝置(例如,存儲器裝置)利用時序與數據信號、數據選通及/或其它信號的相移來執行操作(例如,寫入操作)。dfe可用于維持數個(例如,4個)先前數據位的緩沖器以改進解譯當前位是高還是低的準確性。例如,如果dfe存儲4個先前低數據位,那么數據線(dq)將處于較低電壓電平,且當前數據位將被解譯為相對于所述電平為邏輯高或低。這些多抽頭dfe輸入緩沖器用于允許較小外部數據眼的分辨率。然而,隨著存儲器裝置中的速度增加,用于在正確時間復位dfe的時序變得更加困難。正確時間是在初始數據鎖存器之后且在使用致使數據從輸入緩沖器輸出的輸出時鐘輸出數據之前或之后的某個點處。由于在實施dfe復位時的傳播延遲,可在輸出時鐘的脈沖出現之前復位dfe,特別是在將額外延遲添加到dfe復位以補償高速實施方案的額外輸入緩沖器延遲的情況下。這些傳播延遲可隨著額外緩沖被包含在存儲器裝置中來滿足對存儲器裝置中的更高時鐘速度的需求而增長。然而,如果dfe復位在輸出時鐘脈沖之前傳播到輸入緩沖器/傳播通過輸入緩沖器,那么輸入緩沖器中的數據可能在從輸入緩沖器輸出之前被復位,因此在嘗試捕獲輸入緩沖器中的數據時可能導致數據丟失。

2、本公開的實施例可針對上文提出的問題中的一或多者。

技術實現思路

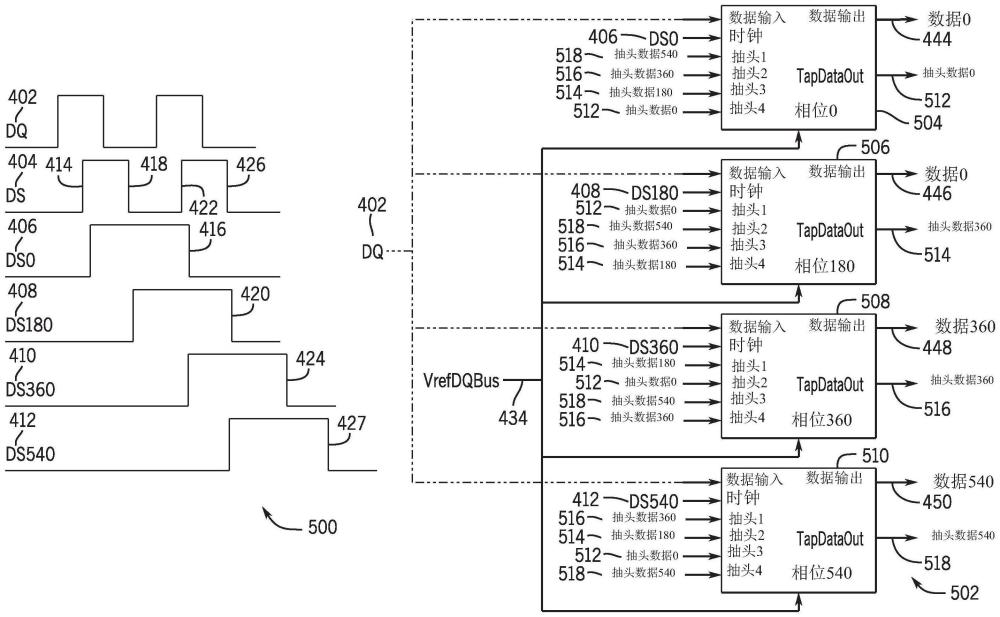

1、本公開的一方面涉及一種存儲器裝置,其包括:判決反饋均衡器(dfe)復位產生器,其經配置以向dfe的復位抽頭傳輸dfe復位信號;及輸入緩沖器,其包括:數據分支,其經配置以從所述輸入緩沖器產生輸出數據以在下游用于所述存儲器裝置中;及dfe復位分支,其經配置以基于所述dfe復位信號來復位所述dfe的所述抽頭,其中所述數據分支及所述dfe復位支路經配置以并行接收分支數據。

2、本公開的另一方面涉及一種半導體裝置,其包括:判決反饋均衡器(dfe)復位產生器,其經配置以向dfe的復位抽頭傳輸dfe復位信號;及輸入緩沖器,其包括:數據分支,其包括第一組電路系統,所述第一組電路系統經配置以接收分支數據且基于所述分支數據來從所述輸入緩沖器輸出數據以在下游用于所述半導體裝置中;dfe復位分支,其包括第二組電路系統,所述第二組電路系統經配置以接收分支數據且基于所述dfe復位信號來復位所述dfe的所述抽頭,其中所述數據分支及所述dfe復位分支經配置以并行接收所述分支數據;及公共鎖存器部分,其經配置以產生所述分支數據。

3、本公開的又一方面涉及一種方法,其包括:在存儲器裝置的輸入緩沖器處接收數據(dq);使用多個鎖存級從所述dq產生分支數據;并行地向所述輸入緩沖器的數據分支及所述輸入緩沖器的判決反饋均衡器(dfe)分支傳輸所述分支數據;使用所述數據分支來至少部分基于所述分支數據來產生所述輸入緩沖器的輸出數據;及使用所述輸入緩沖器的所述dfe分支來至少部分基于所述分支數據來產生用于所述存儲器裝置的dfe的多個抽頭。

技術特征:

1.一種存儲器裝置,其包括:

2.根據權利要求1所述的存儲器裝置,其中使用所述dfe復位分支復位所述抽頭不復位所述數據分支的輸出數據。

3.根據權利要求1所述的存儲器裝置,其中使用所述dfe復位信號復位所述抽頭不復位所述數據分支的任何部分。

4.根據權利要求1所述的存儲器裝置,其中所述輸入緩沖器包括產生所述分支數據的dfe復位插入點的公共部分上游,且所述數據分支不接收所述dfe復位。

5.根據權利要求4所述的存儲器裝置,其中所述公共部分包括經配置以產生所述分支數據的第一一或多個鎖存級及第二一或多個鎖存級。

6.根據權利要求5所述的存儲器裝置,其中所述第一一或多個鎖存級將用于為邏輯高的前一位,且所述第二一或多個鎖存級將用于為邏輯低的所述前一位。

7.根據權利要求5所述的存儲器裝置,其中所述dfe復位分支包括:

8.根據權利要求7所述的存儲器裝置,其中所述數據分支包括第五一或多個鎖存級,所述第五一或多個鎖存級與所述dfe復位分支接收所述第一輸出及所述第二輸出并行接收所述第一輸出及所述第二輸出。

9.根據權利要求8所述的存儲器裝置,其中所述dfe復位分支包括選擇電路系統以在前一位為邏輯高的情況下選擇所述第一輸出,且在所述前一位為邏輯低的情況下選擇所述第二輸出。

10.根據權利要求9所述的存儲器裝置,其中所述選擇電路系統經配置以選擇正值或真值,所述dfe復位分支包括額外選擇電路系統以在所述第一輸出與所述第二輸出之間選擇以產生負值或負的值。

11.根據權利要求9所述的存儲器裝置,其中所述數據分支包括額外選擇電路系統以在所述第一輸出與所述第二輸出之間進行選擇以為所述輸入緩沖器產生不通過dfe復位來復位的所述輸出數據。

12.一種半導體裝置,其包括:

13.根據權利要求12所述的半導體裝置,其中使用所述第二組電路系統復位所述抽頭不復位所述輸出數據。

14.根據權利要求12所述的半導體裝置,其包括包含所述輸入緩沖器的多個輸入緩沖器,其中所述多個輸入緩沖器中的每一輸入緩沖器對應于用于捕獲在所述半導體裝置處從主機裝置接收的數據dq的數據選通dqs的相位。

15.根據權利要求14所述的半導體裝置,其包括中間碼dqs計數器,所述中間碼dqs計數器經配置以在寫入操作的寫入后置碼之后且在后續寫入操作的寫入前置碼之前阻擋可在未知dqs區中產生的偽dqs信號。

16.根據權利要求12所述的半導體裝置,其中:

17.一種方法,其包括:

18.根據權利要求17所述的方法,其包括:

19.根據權利要求17所述的方法,其中所述輸入緩沖器是各自對應于多個dqs相位的不同數據選通dqs的多個輸入緩沖器中的一者。

20.根據權利要求19所述的方法,其包括:

技術總結

本公開涉及具有分支DFE復位路徑的數據輸入緩沖器。提供用于包含判決反饋均衡器DFE復位產生器的存儲器裝置的系統及方法,所述判決反饋均衡器復位產生器經配置以向DFE的復位抽頭傳輸DFE復位信號。所述存儲器裝置還包含輸入緩沖器。所述輸入緩沖器包含數據分支,所述數據分支經配置以從所述輸入緩沖器輸出數據以在下游用于所述存儲器裝置中。所述輸入緩沖器還包含DFE復位分支,所述DFE復位分支經配置以基于所述DFE復位信號來復位所述DFE的所述抽頭。此外,使用所述DFE復位分支復位所述抽頭不復位所述數據分支的輸出數據。

技術研發人員:W·C·沃爾德羅普,南基浚,尹元柱,三堀真吾

受保護的技術使用者:美光科技公司

技術研發日:

技術公布日:2024/10/21

- 還沒有人留言評論。精彩留言會獲得點贊!