芯片、芯片系統和時間戳同步方法與流程

本公開的實施例涉及一種芯片、芯片系統和時間戳同步方法。

背景技術:

1、電子器件需要利用時間戳數據來表征時間,時間戳數據能夠幫助系統用戶實現對時間延遲的感知和測量。在一個多芯片互聯的芯片系統中,為了提高時間延遲的測量精度,需要保證各芯片維持相同的時間戳數據。系統中每個芯片都有自己獨立的時間戳計數器,由于系統初始化時各芯片上時間戳計數器的使能時間不同步和/或各芯片的輸入時鐘來源可能非同源,這可能會導致系統運行過程中各芯片間的時間戳數據產生差異,影響系統用戶計算時間延遲的精度。因此,可以在多芯片互聯系統中引入時間戳同步方案,來解決各芯片間時間戳數據的差異問題。

技術實現思路

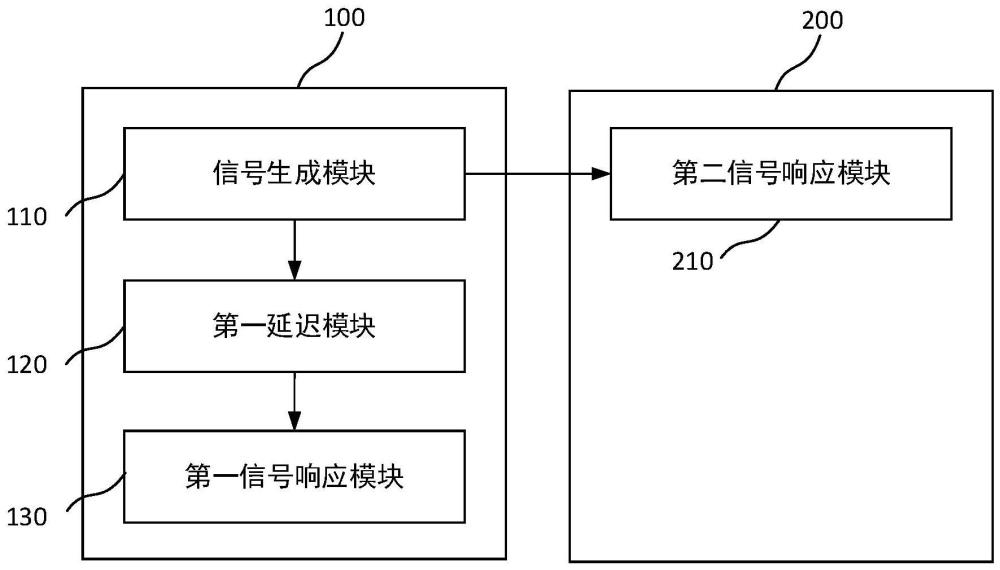

1、本公開至少一個實施例提供一種芯片(第一芯片),其中,所述芯片配置為與另一芯片(第二芯片)通信連接,所述芯片包括:信號生成模塊、第一信號響應模塊和第一延遲模塊,其中,所述信號生成模塊配置為生成同步請求信號,并將所述同步請求信號發送給所述第一信號響應模塊和所述另一芯片,以使所述另一芯片的第二信號響應模塊響應于接收所述同步請求信號記錄所述另一芯片的第二時間戳;所述第一延遲模塊配置為對所述信號生成模塊傳輸至所述第一信號響應模塊的所述同步請求信號進行延遲處理,以得到延遲的同步請求信號;所述第一信號響應模塊配置為響應于接收所述延遲的同步請求信號,記錄所述芯片的第一時間戳,所述第一時間戳和所述第二時間戳用于進行時間戳同步操作。

2、本公開至少一個實施例提供一種芯片(第二芯片),其中,所述芯片配置為與另一芯片(第一芯片)通信連接,所述芯片包括:第二信號響應模塊和第二同步控制模塊,其中,所述第二信號響應模塊配置為響應于接收來自于所述另一芯片的同步請求信號,記錄所述芯片的第二時間戳,并且將所述同步請求信號發送給所述第二同步控制模塊;所述第二同步控制模塊配置為響應于接收所述同步請求信號,從所述第二信號響應模塊獲取所述第二時間戳,以及從所述另一芯片獲取第一時間戳,并基于所述第一時間戳和所述第二時間戳執行時間戳同步操作;其中,所述第一時間戳為所述另一芯片的第一信號響應模塊響應于延遲的同步請求信號而記錄的所述另一芯片的時間戳。

3、本公開至少一個實施例提供一種芯片系統,包括:第一芯片和第二芯片,第一芯片包括信號生成模塊、第一信號響應模塊和第一延遲模塊,第二芯片配置為與第一芯片通信連接,包括第二信號響應模塊和第二同步控制模塊;其中,所述信號生成模塊配置為生成同步請求信號,并將所述同步請求信號發送給所述第一信號響應模塊和所述第二芯片;所述第一延遲模塊配置為對所述信號生成模塊傳輸至所述第一信號響應模塊的所述同步請求信號進行延遲處理,以得到延遲的同步請求信號;所述第一信號響應模塊配置為響應于接收所述延遲的同步請求信號,記錄所述第一芯片的第一時間戳;以及所述第二信號響應模塊配置為響應于接收來自于所述第一芯片的同步請求信號,記錄所述第二芯片的第二時間戳,并且將所述同步請求信號發送給所述第二同步控制模塊;所述第二同步控制模塊配置為響應于接收所述同步請求信號,從所述第二信號響應模塊獲取所述第二時間戳,以及從所述第一芯片獲取所述第一時間戳,并基于所述第一時間戳和所述第二時間戳執行時間戳同步操作。

4、本公開至少一個實施例提供一種時間戳同步方法,用于第一芯片,所述第一芯片配置為與第二芯片通信連接,所述方法包括:生成同步請求信號;將所述同步請求信號發送至所述第二芯片,以使所述第二芯片響應于所述同步請求信號記錄所述第二芯片的第二時間戳;對所述同步請求信號進行延遲處理,以得到延遲的同步請求信號;響應于所述延遲的同步請求信號,記錄所述第一芯片的第一時間戳,所述第一時間戳和所述第二時間戳用于進行時間戳同步操作。

5、本公開至少一個實施例提供一種時間戳同步方法,用于第二芯片,所述第二芯片配置為與第一芯片通信連接,所述方法包括:響應于接收來自于所述第一芯片的同步請求信號,記錄所述第二芯片的第二時間戳;從所述第一芯片獲取第一時間戳,其中,所述第一時間戳為所述第一芯片響應于延遲的同步請求信號而記錄的所述第一芯片的時間戳;基于所述第一時間戳和所述第二時間戳執行時間戳同步操作。

技術特征:

1.一種芯片,其中,所述芯片配置為與另一芯片通信連接,所述芯片包括:信號生成模塊、第一信號響應模塊和第一延遲模塊,其中,

2.根據權利要求1所述的芯片,其中,所述第一延遲模塊配置為使得所述延遲的同步請求信號被所述第一信號響應模塊響應的時間與所述同步請求信號被所述第二信號響應模塊響應的時間的時間差小于時間差閾值。

3.根據權利要求1所述的芯片,其中,所述第一信號響應模塊還配置為響應于所述另一芯片的時間戳獲取請求,將所述第一時間戳發送至所述另一芯片,以使所述另一芯片基于所述第一時間戳和所述第二時間戳進行所述時間戳同步操作。

4.根據權利要求1至3任一項所述的芯片,其中,所述第一信號響應模塊包括:第一信號捕獲模塊和第一記錄模塊,其中,

5.根據權利要求1至3任一項所述的芯片,其中,所述信號生成模塊包括:

6.根據權利要求1至3任一項所述的芯片,還包括:

7.根據權利要求3所述的芯片,還包括:

8.根據權利要求4所述的芯片,還包括:

9.根據權利要求1至3任一項所述的芯片,還包括:

10.一種芯片,其中,所述芯片配置為與另一芯片通信連接,所述芯片包括:第二信號響應模塊和第二同步控制模塊,其中,

11.根據權利要求10所述的芯片,其中,所述延遲的同步請求信號被所述第一信號響應模塊響應的時間與所述同步請求信號被所述第二信號響應模塊響應的時間的時間差小于時間差閾值。

12.根據權利要求10或11所述的芯片,其中,所述第二信號響應模塊包括:第二信號捕獲模塊和第二記錄模塊,其中,

13.根據權利要求12所述的芯片,還包括:

14.根據權利要求12所述的芯片,還包括:

15.根據權利要求14所述的芯片,其中,所述第二同步控制模塊配置為:

16.根據權利要求15所述的芯片,還包括:

17.根據權利要求12所述的芯片,還包括:

18.一種芯片系統,包括:

19.一種時間戳同步方法,用于第一芯片,所述第一芯片配置為與第二芯片通信連接,所述方法包括:

20.一種時間戳同步方法,用于第二芯片,所述第二芯片配置為與第一芯片通信連接,所述方法包括:

技術總結

一種芯片、芯片系統和時間戳同步方法。芯片配置為與另一芯片通信連接,包括:信號生成模塊、第一信號響應模塊和第一延遲模塊,信號生成模塊配置為生成同步請求信號,并將同步請求信號發送給第一信號響應模塊和另一芯片,以使另一芯片的第二信號響應模塊響應于接收同步請求信號記錄另一芯片的第二時間戳;第一延遲模塊配置為對信號生成模塊傳輸至第一信號響應模塊的同步請求信號進行延遲處理,以得到延遲的同步請求信號;第一信號響應模塊配置為響應于接收延遲的同步請求信號,記錄芯片的第一時間戳,第一時間戳和第二時間戳用于進行時間戳同步操作。該芯片可以實現邏輯簡單、功能穩定、且高效的跨芯片時間戳同步。

技術研發人員:董威鋒,葉金才,成園林,劉鵬飛,賈新霞,盧山,王劍

受保護的技術使用者:北京有竹居網絡技術有限公司

技術研發日:

技術公布日:2024/10/21

- 還沒有人留言評論。精彩留言會獲得點贊!